# **REDUCTION OF DELAY AND POWER IN FIR FILTERS USING** EXACT COMMON SUB-EXPRESSION AND GB BASEDMETHOD **USING CSA**

## Arjun M<sup>1</sup>, Mohan H M<sup>2</sup>

<sup>1</sup>PG Student, Department of ECE, T.John Institute of Technology, Karnataka, India <sup>2</sup>Assistant Professor, Department of ECE, T.John institute of Technology, Karnataka, India

## Abstract

Finite impulse response (fir) filters wereconstructed by using multiplication, coefficients and adders. Fir filters are mainly utilized in digital signal processing because of its feed forward features. To decreasedifficulty in circuit, multiple constant multiplier method is preferred much, further to lessen delay, power intake and area in fir filters we use exact common sub-expression method and GB method in this paper along with these approaches, altered carry select adder is also used here which diminishes 50% delay and 15-25% enhancement in power effectiveness related to conventional one.

\*\*\*

Keywords: CSA; FIR Filters; MCM; GBMethod; CSE etc...

## **1. INTRODUCTION**

Many engineering applications related to digital circuits uses multiplication as main computation. Multiplication consists of addition and shift operations, due to the repetition of terms even the small multiplications will lead to more program count. In order to reduce this repetition of terms MCM method is widely used, but MCM technique with adders will not provide good results for delay and power efficiency.

Fir filters developments was did by many researchers after the invention of computational world. Bull and Horrocks method was invented by Dempsteret al in which FIR filter are applied in many advanced fields of science and time was succefully reduced, but it leads into increase of delay and complexityin the circuit.

Hartley suggested the procedure which recognizes common termsidentified as CSD, as a result 50% driveramount was saved and by linking common expressions further 32% redeemable in driveramountwere accomplished. Periodconstants and region were neglected in this study.

All the research papers mentioned above indicatesthe complicationslinking to delay, period and amount of power intake. For this Potokonjak [6] proposed the Multiple Constant Multiplication (MCM) method in February 1996, the Computational Sharing Multipliers (CSHM) was advanced by Park et al by using MCMmethod. Here to shorten add and shift processes, multiplication has been ascended to vector form. But smaller amount power andless amount of delay was not attained due to this drawback. Longrealization of expressions is only cause for all these failures, Aksoy'sintroduced the methodfor removing sub terms in MCMby means of System of Booleanbut then again even it couldn't resist the delay with CSD and binary data.

All the papers which are conversed and studied above went through problems related to delay and power intake. From above literature study, hence practicebyMCMmethodusing GBprocess is proposed. These approaches are also used with Carry Select Adder (CSA) leads to good outcomes. In section 2 the proposed work has been conversed. Also constituents required forbuilding FIR by using CSA is described on this sector. Results part is declared in the section 3.Conclusion and future enhancement of the study is mentioned in section 4.

## 2. PROPOSED WORK

In FIR execution, the study of illustrations shows that partial yields in GB process will give the goodoutcome in terms of area drop at gate level.

D flip-flops are used in MCM procedure to perform shifting process, this technique is unrestricted from hardware has it works on bits parallel system. Hence, in digit-serial MCM design the high-level algorithms are developed for sharing of shift, subtraction and addition actions. From the research it determined that science digit-serial operatives consumes a smaller amount area and are not dependent on the data word length, when related to bit-parallel designs, digit-serial designs offers fewer complexity designs. The GB technique is used for the execution of the concept.

When related to binary, CSD has 33% decrease in non-zero components. Hence to rise the effectiveness of program, Sign Digit (SD) method is utilized. It helps to get high speed arithmetic organization, low power capable, and decline in area in DSP applications.

For executing the circuit of any structure the Boolean function is significantfragment, and Conjunctive Normal Form (CNF) [13] is used to denote the proportional formula... In this paper, DSA technique is used to decrease delay and area successfully. To accomplish the set of goals, previously predefined procedures are used.

Exact Common Sub-expression Elimination (CSE) algorithm

These algorithms can be designed by means of the steps point out below:

- a) Partial expressions are identified.

- b) Boolean network is created.

- c) 0-1 IPL problem is designed.

- d) The lowest area resolution has been determined.

- 1) Development of FIR filter

FIR can be represented as below equation:

$$H(z) = \frac{Y(z)}{X(z)} = \sum_{n=0}^{N-1} h[n] \cdot z^{-n}$$

We get constant accurateness in fir filters related to infinite impulse response filters for the similar order as fir filters are less complex. Hence fir filters are used in different realization approaches. For the purpose of software execution direct and improved designs are used because it is more appropriate related to other realizations.

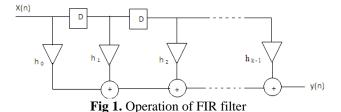

Due to the direct phase features and feed forward application of fir filters, it plays significant role in digital signal processing. Fir filters are constant filters and as high performance in digital domain. Operation of fir filters is presented below in fig1.

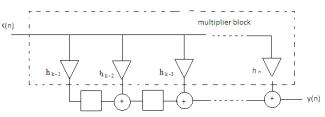

In the above construction hardware is complex, hence altered form of fir filters are used with standard multipliers. Here all the multiplication actions are composed together and named it as multiplier block, where fir filters input and coefficients are multiplied. Itadvances the performance and also complication of the design is reduced considerably because of the constant multiplication.

Fig 2. Multiplier block that accumulates all multiplication actions together

#### 2) CSA

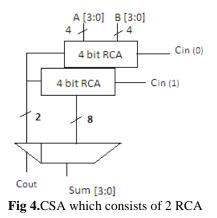

CSA is used to get more precise results compared to previously existing approaches. Carry select adder (CSA) consists of two ripple carry adder(RCA) and a full adder to yield output.

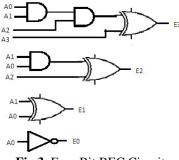

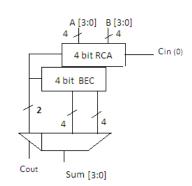

CSA suffers from increased transmission delay. So as an alternative CSA,1 BEC design is placed instead of 1 RCA... For four bit methodresulting Fig. 3 shows the operation inBEC. Ripple carry adder has a composite circuit which results in high propagation delay. Hence two RCA circuits in CSA is substituted by 1 BEC AND 1 RCA, But n+1 bits BEC is necessary in order to replace n bit RCA. The employment of BEC is given,

Fig 3. Four Bit BEC Circuit

First the employment of the CSA using two RCA is done. This operation is shown below. Then one RCA circuit is substituted with BEC circuit inEmployment of CSA with two RCA.

As mentioned up, RCA is substituted with BEC, which eliminates the disadvantage of RCA circuit; hence propagation delay is reduced as preferred from this method.

Fig 5.1 RCA'S is replaced by 1BEC

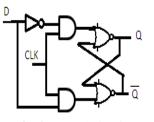

#### 3) D latch

D-latch alters for rising and falling edge of the clock cycle. It is utilized to store the data which is beneficial for fir filter employment. Here d-latch permits the yieldfrom BEC and RCA mixtureand it sent for multiplexer circuit. Delay gets reduced by thebenefits of latch. Latch is placed below the BEC circuit which can be witnessed in fig6.

Fig 6. D Latchcircuit

#### 4) Full adder and subtractor

Full adder and subtractor constituents are utilized for adding and shifting process to carry. Multiple constant multiplication Process is widely used in fir filters. In this method count of variables are reduced and speed of the multiplication increases. And also Set of variables are multiplied with particular constants here. It discovers the common terms in addition and subtraction process of fir filters which will advance the speed of completing task. This in turn decreases delay.

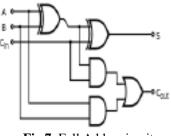

#### 3) Full Adder

Full adder is used in binary number addition, which produces sum and carry as yield. Organization of gate is shown below.it comprises of two inputs A and B, carry if least significant bit is repersented as Cin. output of sum and carry are S ans Cout individually.

Fig 7. Full Adder circuit

The one bit adders are arranged in cascade order to raise number of bits (2n) which yields desired output. Carry and sum illustration and its relation are shown below.

$$Sum=2 \times Cout+S$$

(3)

The employment of full adder is as (4) and (5),

$$S=A \oplus B \oplus Cin \qquad (4)$$

$$Cout=(A.B)+(Cin.(A \quad (5)$$

$\oplus B))$

In this execution, we can replace XOR gate by OR gate before getting carry-out output, which is done without varying resulting logic.

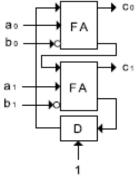

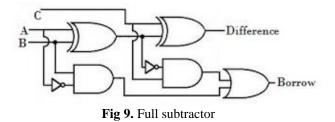

b) Full Subtractor

Fig 8. Subtractor circuit

To carry subtraction operation 2's complements technique is used. itneedsd flip flops to initialize with high and d inverter action as to be done. Employment of subtraction operation with 2's complements technique is presented in fig8 subtractor is utilized to carry subtract proceduresby three bits E,F,G which is displayed in fig. it contains 3 inputs E, F and G and 2outcomes which are difference and borrow respectively.

logic diagram is shown below,

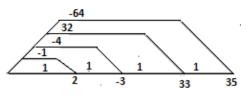

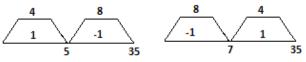

Multiplication by means of GB method is area and time consuming, hence process mentioned below in fig will give exact outcome and takes less area.

CSA circuit is feed with this equation more, which produces the final results. Xilinx 14.2 is used to run the algorithm and RTL graph of GB methodincludingCSA is observed, project summary is observed.

Fig. 10. Common representation of GB

Fig. 11. ShortenedConstruction of GB graph

#### RESULTS

The main consideration in this paper is about the decline in the intake of the power ,delay along with the decline in area. In order to simplify addition BEC method is used along with GB method which uses less computational incomes and produces goodyield. In VHDL coding BEC method is employed and Xilinx software is used to execute it. modification the 2methods (CSE, GB) can be seen in below mentioned screen picture which illustrates count by cycle's consumed and alsovolume of data spent from the individual terms.

| Current Simulation<br>Time: 1000 ns |     | 900 ns 910 ns 920 ns 930 ns 940 ns 950 ns 960 ns 970 ns 980 ns 990 ns 1000 ns |

|-------------------------------------|-----|-------------------------------------------------------------------------------|

|                                     |     |                                                                               |

| ■ 🕅 x[3:0]                          | 4   | 4                                                                             |

| <mark>ð</mark> [] x[3]              | 0   |                                                                               |

| <mark>₀</mark> ,[ x[2]              | 1   |                                                                               |

| <mark>ð</mark> ,[ x[1]              | 0   |                                                                               |

| <mark>6</mark> ,[] x[0]             | 0   |                                                                               |

| 🗖 🚮 y1[7:0]                         | 116 | 116                                                                           |

| <mark>ə</mark> [] y1[7]             | 0   |                                                                               |

| y1[6]                               | 1   |                                                                               |

| <mark>ð</mark> ,[] y1[5]            | 1   |                                                                               |

| <b>6</b> [] y1[4]                   | 1   |                                                                               |

| <mark>ð</mark> ,[] y1[3]            | 0   |                                                                               |

| <mark>6,[]</mark> y1[2]             | 1   |                                                                               |

| <b>6</b> [] y1[1]                   | 0   |                                                                               |

| <b>0</b> [] y1[0]                   | 0   |                                                                               |

|                                     | 172 | 172                                                                           |

|                                     |     |                                                                               |

|                                     |     |                                                                               |

|                                     |     |                                                                               |

|                                     |     | Eta 12 Outcome of CD has considering CSA DEC                                  |

Fig 12. Outcome of GB by considering CSA, BEC

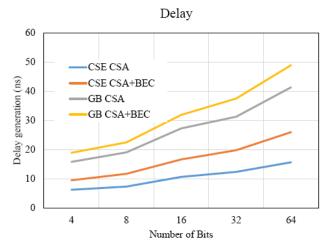

Although the GB algorithm has more number of variables the outcomes showed least intake of data is achieved. Additional outcomes obtained from employment of below 2approaches of FIR on Xilinx is displayed in the diagram below.

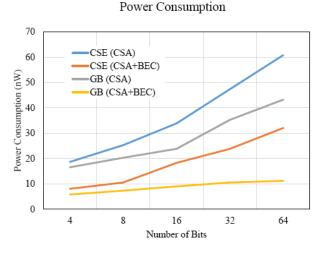

In Fig. 13 and Fig. 14, for CSA and CSA + BECconstituents, the 2systems (CSE, GB) with interruption, space, intake of power and memory were plotted respectively. The usage and intake of various parameters of FIR filter employment using two different methods with two

different constituents is shown in the above graph. The suggested method provides 50% fall in delay; it is shown in Fig. 13.

Over all it was evident that the area utilization was reduced by 5% and power consumption by 55%. It was also found that compared to formerapproaches or structures which had more step utilization in GB method, the memory consumption was declined by 4%.

## CONCLUSION

In any VLSI and communication circuits FIR filters are applied, which is an important part of the DSP system. The usage of RCA and BEC in CSA along with GB method gives an improved result which is the focus of the existing result. When compared with CSA the delay is reduced by 48% also 49% CSE, GB constituents. By Using CSA, the power effectivenesshas enhanced by 55% ,65% by CSE plus GB individually. The present investigation is limited to simulation. More impact on this research is seen when experimental execution on hardboard is done.

### REFERENCES

[1]. J. McClellan, T. Parks, and L. Rabiner, "A computer program for designing optimum FIR linear phase digital filters," *Audio Electroacoust.* ..., 1973.

[2]. A. G. Dempster, S. Member, M. D. Macled, and A. G. Representation, "Blocks in FIR Digital Filters," vol. 42, no. 9, 1995.

[3]. W. L. Gallagher and E. E. Swartzlander, "High Radix Booth Multipliers Using Reduced Area Adder Trees," pp. 545–549, 1995.

[4]. R. I. Hartley, "Subexpression Sharing in Filters Using Canonic Signed Digit Multipliers," vol. 43, no. October, 1996.

[5]. H. T. Nguyen and A. Chatterjee, "Number-Splitting with Shift-and-Add Decomposition for Power and Hardware Optimization in Linear DSP Synthesis," vol.8, no. 4, pp. 419–424, 2000.

[6].M. Potkonjak, M. B. Srivastava, and A. P. Chandrakasan, "Multiple Constant Multiplications: Efficient and Versatile Framework and Algorithms for Exploring Common Subexpression Elimination," *IEEE Trans. Comput. Des.Integr. CIRCUITS Syst.*, vol. 15,no. 2, 1996.

[7]. H. Applications, J. Park, W. Jeong, H. Mahmoodimeimand, S. Member, Y. Wang, H. Choo, and K. Roy, "Computation Sharing Programmable FIR Filter for," vol. 39, no. 2, pp. 348–357, 2004.

#### BIOGRAPHIES

**Mr. Arjun** received BE Degree in Electrical and Electronics Engineering from the Visvesvaraya Technological University. He is a student of M.Tech in Vlsi Design and Embedded System, VTU, Belgaum. Area of interest is in Vlsi design circuits and digital circuit design.

**Mr.Mohan H M** is working as Assistant Professor in the department ofECE at T.John Institute of Technology Bangalore. HE has obtained her M.Tech Degree in Vlsi Design and Embedded System from VTU Belgaum,his area of interest is in VLSI Design circuits and Embedded systems.