# PERFORMANCE ANALYSIS AND IMPLEMENTATION OF MODIFIED SDM BASED NoC FOR MPSoC ON SPARTAN6 FPGA

Y. Amar Babu<sup>1</sup>, G.M.V.Prasad<sup>2</sup>

<sup>1</sup>Department of Electronics & Communication Engineering, LBR College of Engineering <sup>2</sup>Principal & Professor in ECE, B.V.C Institute of Technology & Science

### Abstract

To meet todays demanding requirements lowpower consumption, high performance while maintaing flexibility and scalability, system-On-Chip will combine several number of processors cores and other IPs with network-On-chip. To implement NoC based MPSoC on an FPGA, NoCs should provide guaranteed services and be run-time reconfigurable. Current TDM and SDM based NoCs takes more area and would not support run-time reconfiguration. This paper presents modified spatial division multiplexing based NoC on FPGA, in this we have modified complex network interface and proposed flexible network interface and efficient SDM based NoC. This architecture explored feasibility of connection requirements from IP cores during run-time.

Keywords: NoC, MPSoC, FPGA, NoCs, SDM Based NoC

### I. INTRODUCTION

According to moore's law chip density is increasing exponentially, allowing multiple processor system-on-chip can be implemented on single FPGA. The main challenge in todaysMPSoC is communication architectures among processors. The conventional way of utilizing bus architectures for inter IP core communication has many limitations. Mainly, it does not scalable well with increasing soft cores on single FPGAs. Next, it is tough to couple high computation and demanding communication of the MPSoC platform leading to expensive design flow with long design time. Network on chip have become only alternative to solve these problems.

Most of existing NoC offers and relay on a best effort service those are depends on packet switing technique. Examples of packet based NoCs are MANGO and Xpipes[3]. Another class of NoCsare based on circuit switching technique whose methodology is to fix the entire path from source node to the destination node before coming data from thesource node. PNoC and SPIN[4], based on circuit switching method. Todays multimedia based system demands predictable performance as node link between soft cores are tightly time constrained. For such multi-core systems, it is compulsory to provide guaranteed throughput service before run-time. To meet these constraints, link allocation should be done in advance during design flow time.

TDM based NoC provides guaranteed throughput where different time slots are used on the same link. One demerit of TDM is that router switching configuration need to be changed every time slot. This feature requires time slot tables that needs area and consume power in every router. Nostrum and AEthereal are based on TDM NoCs, those architectures has to maintain time slot tables. Spatial division multiplexing is best method where node links, which inter connect the routers are allocated to different links. Each link has flexible number of wires to assigned to them. These rialised data sent from sender on the wires allocated and those are deserialised by the receiver before forwarding to the IP core. The main merit of SDM over other technique is that it removes the need of time slot tables thus power optimised but complexity is moved to the serializer and deserializer of network interface.

In this paper, we provide best methods to the above problems. We have proposed a novel design and modified architecture for network interface to handle the serializer and deserialiser complexity that is common in SDM based NoC[7]. A simple router with less complexity is proposed which uses lower area at the cost of routing flexibility. This mainly reduces the problem of reordering the data when data arrive at the destination Network Interface.Our design flow provides dynamically reconfiguring the NoC with different link setups during run-time. We have modeled VHDL code for SDM based NoC.We have connected microblazes in a MPSoC using modified SDM based NoC with Xilinx EDK and a working prototype has been implemented on a xilinx spartan6 FPGA SP605 Evaluation board(SP605). The softcoresmicroblazes were used to evaluate the dynamic reconfiguration of the NoC as well as to communicate data between each other.

#### **II. MODIFIED** SDM BASED NoC **ARCHITECTURE**

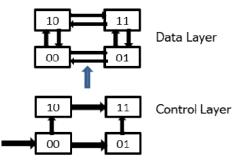

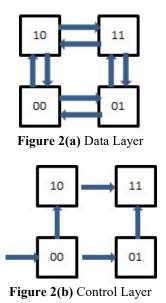

The proposed architecture has been modeled as dual layer structure where first layer is responsible for data transfer while the second layer is the responsible for configuring router links. The network topology is used for the architecture is mesh which is best for multimedia applications.Figure1 shows basic architecture of modified SDM based NoC.

Figure 1: Modified SDM based NoC

#### A. Dual layer structure

The second layer is simple network mainly used to program the NoC as application demanded bandwidth. To program the NoC, links between router should be fixed as soft cores which requires data from other IP or soft cores. Number of programming byte required to program the NoC depends on size of mesh network(i.e 2x2 to maximum 7x7) that can mapped on to target FPGA. For each router there will be one soft IP which internally connected through network interface. Network interface in each IP serializes soft IP data from sender and deserializes at receiver side in order to receive data from source IP. All routers and soft IP with network will place in first layer which is responsible to transfer data from any source node to any destination node through router links. Designer fix the number of wire required to transfer data from source node to destination node as per bandwidth requirements which is programmable at design time.Figure 2 shows Dual layers in detail.

#### B. Modified Network Interface

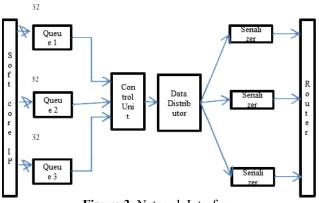

The modified network interface for the spatial division multiplexing based network on chip has special control block that will be used to control in coming 32 bit data from different channels of soft IP cores. This intelligent control unit replaces multiple data distributors at transmitter side and multiple data collectors at receiver side with only one data distributor and one data collector. Proposed control unit can be used for fault tolerance to minimize faults at transmitter and receiver blocks of network interface. The modified network interface has many features, one of the feature is huge area saving that main problem in any Network on chip architectures and fault tolerance that is very demand for multi-core system-on-chip in embedded applications. We have modified 32 bit to 1 bit serializerwith intelligent control unit in network interface. Figure 3 shows Network Interface.

Figure 3. Network Interface

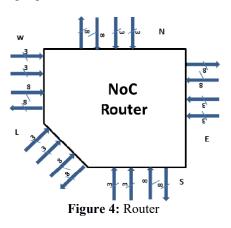

#### C. Router for modified SDM based NoC

We have targeted xilinx FPGA to implement SDM based NoC for MPSoC platform, so router architecture modified just like architecture of xilinx switch by avoiding unnecessary complex logic. In modified router for proposed network-on-chip has five port which includes north, south, east, west and local. Soft IP cores are connected through local port. From local port designer can send data to adjacent router through other four ports. This feature is very unique when compared with any other Network-on-chip architectures. Which provides more flexibility, scalability and huge area saving. Each port size can be design parameter which can be fixed at design time depending on application bandwidth demand.Figure4 shows router architecture in detail. Each side has one input port of size 8 bit, one output port of size 8 bit, one out allocated input port of size 3 bits and one out allocated input index port of size 3. The size of out allocated input size 3 bit because in this only 5 possible direction data can be sent from any side. The size of out allocated input index depends on size if input port and output port on each side.

#### **III. RESULTS**

#### A. Simulation Results

We have setup 2x2 NoC architecture with proposed blocks which are modeled using VHDL and simulated using xilinx ISE simulator ISIM. Figure shows network interface results and data sent from transmitter of network interface and data received from soft IP core into receiver of network interface. Figure also shows top level 2x2 NoC architecture results with all four routers.

| lla ck                          |        |   |

|---------------------------------|--------|---|

| 1 rst                           |        |   |

| oute_0_allocatedinput[2:0]      | 0\1\5\ | 3 |

| oute_0_allocatedinputindex[2:0] |        | 0 |

| oute_1_allocatedinput[2:0]      | 0\1\5\ | 3 |

| oute_1_allocatedinputindex[2:0] | 0      | 1 |

| oute_2_allocatedinput[2:0]      | 0\1\5\ | 3 |

| oute_2_allocatedinputindex[2:0] | 0      | 2 |

| oute_3_allocatedinput[2:0]      | 0\1\5\ | 3 |

| oute_3_allocatedinputindex[2:0] | (0)X   | 3 |

| oute_4_allocatedinput[2:0]      | 0\1\5\ | 3 |

| oute_4_allocatedinputindex[2:0] | 0      | 4 |

| oute_5_allocatedinput[2:0]      | 0 1 5  | 3 |

| oute_5_allocatedinputindex[2:0] | 0      | 5 |

Figure 5. Simulation Results

#### B. Synthesis Results

For our experimental test setup 2x2 modified SDM based NoC for MPSoC platform synthesis reports are generated using xilinx synthesis tool XST. Figure shows synthesis report which has available resource on spartan6 FPGA and used for our test setup and percentage utilization of available resources. Our report concludes that area is optimized at network interface level and router side which can be compared with any other network-on-chip architectures for area optimization

| Table : Synthesis Report   |      |           |             |  |  |  |

|----------------------------|------|-----------|-------------|--|--|--|

| Device Utilization Summary |      |           |             |  |  |  |

| Logic Utilization          | Used | Available | Utilization |  |  |  |

| Number of Slice            | 6062 | 54576     | 11%         |  |  |  |

| Registers                  |      |           |             |  |  |  |

| Number of Slice            | 5257 | 27288     | 19%         |  |  |  |

| LUTs                       |      |           |             |  |  |  |

| Number of fully used       | 2457 | 8862      | 27%         |  |  |  |

| LUT-FF pairs               |      |           |             |  |  |  |

| Number of bonded           | 288  | 296       | 97%         |  |  |  |

| IOBs                       |      |           |             |  |  |  |

| Number of                  | 2    | 16        | 12%         |  |  |  |

| BUFG/BUFGCTRLs             |      |           |             |  |  |  |

Table : Synthesis Report

#### C. Implementation Results

We have integrated proposed modified SDM based NoC for MpSoC platform with four microblaze soft xilinx IP RSIC cores and 9 Fast Simplex Links(FSL) using Xilinx Embedded Development Kit (EDK) 13.3 ISE design suite. Figure shows device utilization summary after implementation. Table I shows device utilization summary of proposed modified SDM based NoC.

| ry |

|----|

| ſ  |

| <b>Device Utilization Summary</b>    |      |           |             |  |  |  |

|--------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                    | Used | Available | Utilization |  |  |  |

| Number of Slice<br>Registers         | 1321 | 54576     | 2%          |  |  |  |

| Number of Slice<br>LUTs              | 1645 | 27288     | 6%          |  |  |  |

| Number of fully used<br>LUT-FF pairs | 999  | 1967      | 50%         |  |  |  |

| Number of bonded<br>IOBs             | 103  | 296       | 34%         |  |  |  |

| Number of<br>BUFG/BUFGCTRLs          | 1    | 16        | 6%          |  |  |  |

#### IV. PERFORMANCE ANALYSIS

To analyze the performance of proposed NoC architectures on spartan6 FPGA we have selected some case studies which includes Advanced Encryption Standard(AES) algorithm, JPEG compression ,JPEG2000 compression and H263 video compression standards. We have evaluated the application programs on proposed NoC architecture and other well popular TDM based NoCs, SDM based NoCs,Shared bus architectures and Advanced eXtensible Interconnect (AXI) architecutres and compared. Our NoC architectures shows better results than other popular architectures in terms of area, power, execution time and reconfiguration time.

#### Table I: Device Utilization In Slices

| Application | Propose<br>d NoC<br>architect<br>ure | SDM<br>based<br>NoC | TDM<br>based<br>NoC | PLB<br>Shared<br>bus | AXI<br>architec<br>ture |

|-------------|--------------------------------------|---------------------|---------------------|----------------------|-------------------------|

| AES         | 6000                                 | 6500                | 7250                | 6250                 | 6450                    |

| JPEG        | 6300                                 | 7000                | 7780                | 6700                 | 6900                    |

| JPEG2000    | 7000                                 | 7500                | 8300                | 7400                 | 7600                    |

| H263        | 7900                                 | 8200                | 9000                | 8200                 | 8500                    |

Table II: Power Consumption

| Application | Proposed<br>NoC<br>architecture | SDM<br>based<br>NoC | TDM<br>based<br>NoC | PLB<br>Shared<br>bus | AXI<br>architecture |

|-------------|---------------------------------|---------------------|---------------------|----------------------|---------------------|

| AES         | 200mW                           | 250mW               | 300mW               | 400mW                | 390mW               |

| JPEG        | 236mW                           | 290mW               | 320mW               | 410mW                | 400mW               |

| JPEG2000    | 300mW                           | 360mW               | 390mW               | 490mW                | 480mW               |

| H263        | 435mW                           | 450mW               | 490mW               | 560mW                | 550mW               |

| Architectures |              |       |       |        |              |

|---------------|--------------|-------|-------|--------|--------------|

| Application   | Proposed     | SDM   | TDM   | PLB    | AXI          |

|               | NoC          | based | based | Shared | architecture |

|               | architecture | NoC   | NoC   | bus    |              |

| AES           | 2s           | 4.5s  | 6s    | 59s    | 50s          |

| JPEG          | 3s           | 6.3s  | 8s    | 90s    | 80s          |

| JPEG2000      | 4s           | 7s    | 9s    | 120s   | 90s          |

| H263          | 5s           | 8s    | 12s   | 200s   | 170s         |

## Table III: Execution Time Of Application On Test Architectures

#### V. CONCLUSION

In this paper, we have proposed a novel design and flexible network interface architecture for existing SDM based NoC to improve performance and provide guaranteed service for multimedia applications. This architecture saves huge area and required only 5% of existing architectures. In future, multiple applications can be evaluated concurrently on modified SDM based NoC to explore high scalability and performance.

#### REFERENCES

[1] International Technology Roadmap for Semiconductors: Semiconductor Industry Association, Dec 2015.

[2] R. H. Havemann, and J. A. Hutchby, "High Performance Interconnecs: An Integration Overview", Proceedings of the IEEE, vol. 89, No. 5, May 2001

[3] K. Goossens, J. Dielissen, and A. Radulescu, "Æthereal network on chip: concepts, architectures, and implementations," IEEE Design & Test of Computers, vol. 22, pp. 414-21, 2005.

[4] E. Bolotin, I. Cidon, R. Ginosar, and A. Kolodny, "QNoC: QoS architecture and design process for network on chip," Journal of Systems Architecture, vol. 50, pp. 105-128, 2004.

[5] D. Bertozzi, A. Jalabert, S. Murali, R. Tamhankar, S. Stergiou, L. Benini, and G. De Micheli, "NoC synthesis flow for customized domain specific multiprocessor systems-on-chip," IEEE Transactions on Parallel and Distributed Systems, vol. 16, pp. 113-129, 2005.

[6] T. Bjerregaard and J. Sparso, "A router architecture for connection-oriented service guarantees in the MANGO clockless network-on-chip," in Proceedings -Design, Automation and Test in Europe, DATE '05, 2005, pp. 1226-1231.

[7] C. Hilton and B. Nelson, "PNoC: A flexible circuitswitched NoC for FPGA-based systems," IEE Proceedings: Computers and Digital Techniques, vol. 153, pp. 181-188, 2006.

[8] D. Castells-Rufas, J. Joven, and J. Carrabina, "A validation and performance evaluation tool for ProtoNoC," in 2006 International Symposium on System-on-Chip, SOC, 2006.

[9] A. Lines, "Asynchronous interconnect for synchronous SoC design," IEEE Micro, vol. 24, pp. 32-41, 2004.

[10] M. Millberg, E. Nilsson, R. Thid, and A. Jantsch, "Guaranteed bandwidth using looped containers in

temporally disjoint networks within the Nostrum network on chip," in Proceedings - Design, Automation and Test in Europe Conference and Exhibition, 2004, pp. 890-895.

[11] A. Leroy, D. Milojevic, D. Verkest, F. Robert, and F. Catthoor, "Concepts and implementation of spatial division multiplexing for guaranteed throughput in networks-on-chip," IEEE Transactions on Computers, vol. 57, pp. 1182-1195, 2008.

[12] J. Rose and S. Brown, "Flexibility of interconnection structures for field programmable gate arrays," IEEE Journal of Solid-State Circuits, vol. 26, pp. 277-282, 1991.

[13] A. Kumar, S. Fernando, Y. Ha, B. Mesman, and H. Corporaal, "Multiprocessor system-level synthesis for multiple applications on platform FPGA," in Proceedings - 2007 International Conference on Field Programmable Logic and Applications, FPL, 2007, pp. 92-97.

[14] A. Javey, J. Guo, M. Paulsson, Q. Wang, D. Mann, M. Lundstrom, and H. Dai. High-field quasiballistic transport in short carbon nanotubes. Physical Review Letters, 92(10), 2004.

[15] V. Agarwal, M. S. Hrishikesh, S.W. Keckler, and D. Burger. Clock rate versus ipc: the end of the road for conventional microarchitectures. In ISCA '00: Proceedings of the 27th Annual International Symposium on Computer Architecture, pages 248.259. ACM Press, 2000.