# **CASCADED H-BRIDGE MULTILEVEL INVERTER IN A THREE** PHASE ELEVEN LEVEL

## Aditya Parashar<sup>1</sup>, Praveen Bansal<sup>2</sup>

<sup>1</sup>Electrical Engineering, MITS gwalior, Madhya Pradesh, India <sup>2</sup>Professor, Electrical Engineering, MITS gwalior, Madhya Pradesh, India

## Abstract

This paper essentially concentrates on the design and implementation of a unique topology for a three phase eleven level cascaded H-bridge multilevel cluverter by employing different kinds of switching schemes. The basic purpose of this paper is to enhance the number of voltage level at the output without addition of any complexity to power circuit.

The main advantages of this proposed topology is to scale down the THD and reducing electromagnetic interface EMI generation and high voltage with very close to sine waveform. In this paper, severel kinds of carrier pulse width modulation techniques are proposed as which scale down the total harmonic distortion and improve the out voltage from the proposed topology and POD modulation techniques reduce the THD. A number of H-bridge arranged in cascaded to increase the voltage level with the different switching schemes analyzed in this paper. It is observed that this new topology can be recommended to three phase eleven level cascaded H-bridge inverter for the best and optimum performance over the conventional methods. This performance in optimized in the eleven level of inverter.

Improving the fundamental waveforms and reducing the total harmonic distortion by using 60 IGBTs and switching is arranged by a topology in cascaded manners.

The simulation model is produced by MATLAB2009 software version.

Key Words: Cascaded H-bridge multilevel inverter, different phase pulse width modulation, total harmonic distortionTHD. EMI

\_\_\_\_\_\_\*\*\*\_\_\_\_\_\_\_\*\*\*

**1. INTRODUCTION**

A multilevel inverter is a semiconductor based power electronic device that is used for high-power high-voltage applications such as Uninterruptible power supplies and flexible FACTs. Whereas conventional two level inverter have some limitations in high-power and maximum voltage applications through switching losses and power ratings [1-2]. Multi-level power conversion is allowed for more than two voltage levels to achieve smoothen and minimum distorted dc to ac power conversion and it can generate a multiple-step voltage waveform with less

distortion, less switching frequency and higher efficiency. The stepped waveforms are fabricated by multiple voltage levels produced by the appropriate connection of the load. This connection is performed by the appropriate switching in the power semiconductors. To obtain a quality output voltage waveform they require high switching frequency along with different pulse-width modulation strategies [3]. Multi-level inverter provides several advantages over twolevel inverter so improve the output voltage waveform, minimized (dv/dt) voltage strain on the load and also reduces electromagnetic interference troubles, but it has some demerits. One of the most obvious demerit is the requirement of higher number of power semiconductor switches. Every switch requires a gate driver circuit, therefore maximize the complexity and size of the entire circuit [4]. Lower voltage rated switches can be used in multi-level inverter rather of greater number of semiconductor switches which can be minimized cost of the semiconductor switches as compared to two level inverters. The multilevel cascaded H-bridge (CHB) inverter shown in Figure 2.1 is one of the popular inverter topologies for high-power applications due to its high voltage operating capability, low dv/dt with reduced total harmonic distortion (THD) and modular structure for reduced manufacturing cost [5]. The conventional modulation schemes for the CHB multi level inverter including carrier based sinusoidal modulations with phase opposition disposition techniques (PODPWM) [6, 7]. The level-shifted modulation schemes have a good THD profile, but suffer from unbalanced power distribution [8-10], whereas the phase shifted schemes are simpler but produce higher THD[8]

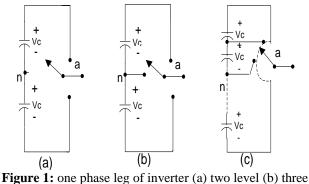

level (c) n-levels

#### **1.1 Equivalent Representation**

An equivalent representation of one phase leg of inverter with different levels shown in figure 1, and power semiconductors is represented by ideal switches with several of positions [3].

There are different conventional multi-level inverters topologies are neutral point- clamped, flying capacitors (capacitor clamped), and cascaded H-bridge (CHB). In 1981 Nabae

Phase opposite disposition PWM scheme offers great advantages such as improved output voltage waveforms, lower EMI, and minimized THD in comparison of other PWM switching schemes.

## 2. PROPOSED TOPOLOGY

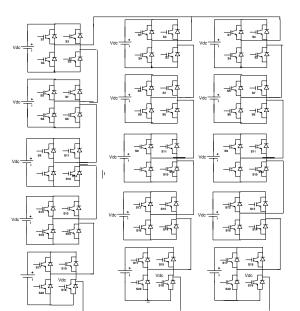

This topology requires sixty semiconductor switches and fifteen isolated dc voltage sources Vdc shown in fig 2.1

#### OPERATION OF THREE-PHASE ELEVEN-LEVEL INVERTER ARRANGED IN CASCADED MANNER

Operation of the three-phase eleven-level inverter with CHB topology is easily explained with the help of fig. 1.2 Whenswitches

\$1,\$2,\$6,\$8,\$10,\$12,\$14,\$16,\$18,\$20,\$21,\$22,\$26,,\$28,\$ 30,\$32,\$34,\$36,\$38,\$40,\$41,\$42,\$46,\$48,\$50,\$52,\$54,\$5 6,\$58,\$60 are turned on the output voltage will be "Vdc" (i.e., level 1). The output voltage will be "+2Vdc" (i.e., level 2) when switches \$1, \$2, \$5, \$6, \$10, \$12, \$14, \$16, \$18, \$20, \$21, \$22, \$25, 26, \$30, \$32, \$34, \$36, \$38, \$40, \$41, \$42, \$45, \$46, \$50, \$52, \$54, \$56, \$58, \$60are turned "on". Similarly output voltage will become "5Vdc" (i.e. level5). When switches \$1, \$2, \$5, \$6, \$9, \$10, \$13, \$14, \$17, \$18, \$21, \$22, \$25, \$26, \$29, \$30, \$33, \$34, \$37, \$38, \$41, \$42, \$45, \$46, \$49, \$50, \$53, \$54, \$57 and \$58. When the switches \$2, \$4, \$6, \$8, \$10, \$12, \$14, \$16, \$18, \$20, \$22, \$24, \$26, \$28, \$28, \$30, \$32, \$34, \$36, \$36, \$38, \$40, \$42, \$44, \$46, \$48, \$50, \$52, \$54, \$56, \$58 and \$60 "on" the output voltage is zero (i.e., level 0).

S3, S4, S7, S8, S11, S12, S15, S16, S19, S20, S23, S24, S27, S28, S31, S32, S35, S36, S39, S40, S43, S44,S47,S48,S51,S52,S55,S56,S59 and S60 turn negative half cycle can be generated across load. The voltage blocking capacity for every switch is Vdc [2]. The operation of this topology can also be easily understood by mode of operation of single-phase eleven-level inverter shown in figure 2. Each voltage source "Vdc" is required 100V. There are eleven sufficient switching modes in generating the multistep levels for a eleven-level inverter.

Figure 2.1: cascaded arrangement of three phase eleven level multilevel inverter

#### 3. MODULATION STRATEGIES

There are different pulse width modulations with different phase relationships.

- Phase disposition pulse width modulation (PD PWM):-In phase disposition pulse width modulation strategy, where all carrier waveforms are in same phase.

- Phase opposition disposition pulse width modulation (POD PWM):- pulse width modulation (PS PWM):-Fig.3.1 shows the carrier Phase-opposition pulse width modulation strategy. In phase opposition disposition pulse width modulation strategy, where all carrier waveforms above zero reference are in phase and below zero reference are 180° out of phase.

- Alternate phase opposition disposition pulse width modulation (APODPWM):- In alternate phase opposition disposition PWM scheme, every carrier waveform is out of phase with its neighbor carrier by <sup>0</sup>/<sub>180</sub>

- Phase-shifted A carrier phase shifted PWM for multilevel inverter is utilized to generate the stepped multilevel

- output voltage waveform with lower % THD. In proposed, before implementing the Multicarrier PWM Techniques, the gating signals of multi-level inverter switches are generated by comparing sinusoidal reference wave with triangular carrier waves (N-1=3) with 120<sup>0</sup> phase displacement and a constant value at specific intervals of time

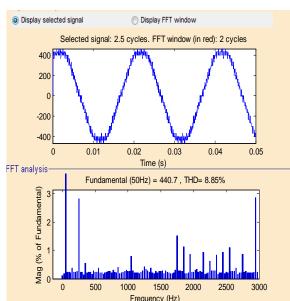

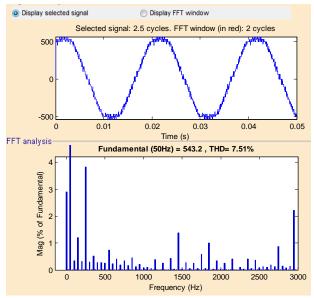

# **3.1 FFT** analysis of a three phase nine level inverter CHB) shown below.

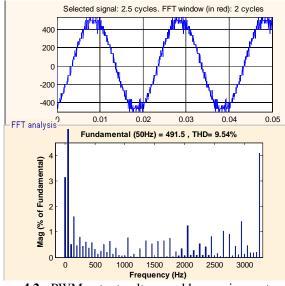

This performance in enhanced in the eleven level of inverter Improving the fundamental waveforms and reducing the total harmonic distortion by using 60 IGBTs and switching is arranged by a topology in cascaded manners

**Figure .2:** PWM output voltage and harmonic spectrum in three phase nine level CHB inverter (Modulation index1.2)

**Figure 4.2:** PWM output voltage and harmonic spectrum in three phase eleven level CHB inverter (Modulation index 1)

| Inverter type                            | NPC            | Flying           |               |           |

|------------------------------------------|----------------|------------------|---------------|-----------|

| inverter type                            | NFC            | capacitor        | cascade       | Proposed  |

| Main switches                            | 2(N-1)         | 2(N-1)           | 2(N-1)        | (N-1)+4   |

| Main diodes                              | 2(N-1)         | 2(N-1)           | 2(N-1)        | (N-1)+4   |

| Clamping diodes                          | 2(N2)<br>(N-1) | 0                | 0             | 0         |

| DC bus<br>Capacitor/Isolated<br>supplies | (N-1)          | (N-1)            | 3(N1)/2       | (N-1)/2   |

| Flying capacitors                        | 0              | (N-1)<br>(N-2)/2 | 0             | 0         |

| Total numbers                            | (N1)<br>(2N+1) | (N1)<br>(N+8)/2  | 11/2<br>(N-1) | (5N+11)/2 |

**TABLE I:** NUMBER OF COMPONENTS:- The number of required components for single-phase eleven level inverter is shown in Table I

**Figure 4.2:** PWM output voltage and harmonic spectrum in three phase eleven level CHB inverter (Modulation index 1.2)

## 4. CONCLUSION

Multi level cascaded H bridge inverters from 7- levels to 11levels have been simulated using MATLAB/Simulink. The following conclusions can be made from the analysis. If number of level increases, the THD content approaches to small value as gestate. Hence it eliminates the requirement of filters. Though, THD decreases with increase in number of levels, some lower or higher harmonic contents persist prevalent in each level. These will be more dangerous in induction drives. Hence the future work may be focalized by applying closed loop control with suitable harmonic elimination.

| <b>TABLE 2:</b> Percent THD comparision for different level |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|

| and different M.I                                           |  |  |  |  |

| and different will |         |        |  |  |

|--------------------|---------|--------|--|--|

| MODULATION         | PWM     | PWM    |  |  |

| INDEX              | %THD    | %THD   |  |  |

|                    | FOR 11- | FOR 9- |  |  |

|                    | LEVEL   | LEVEL  |  |  |

|                    |         |        |  |  |

| 0.92               | 13.29   | 15.76  |  |  |

|                    |         |        |  |  |

| 0.95               | 12.10   | 14.76  |  |  |

|                    |         |        |  |  |

| 0.99               | 11.31   | 13.28  |  |  |

|                    |         | - · -  |  |  |

| 1                  | 9.54    | 12.73  |  |  |

| -                  |         |        |  |  |

| 1.2                | 7.51    | 8.85   |  |  |

| 1.2                | /       | 0.05   |  |  |

|                    |         |        |  |  |

## REFERENCES

- S. Daher, J. Schmid, and F. L. M. Antunes, "Multilevel inverter topologies for stand-alone PV systems," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2703–2712, Jul. 2008.

- [2]. Hemant Joshi, P. N. Tekwani and Amar Hinduja Kolorrol "Multilevel Inverter For Induction Motor Drives Using RV Topology," IEEE Trans. Ind. 2010.

- [3]. Jose Rodriguez, Jih-Sheng Lai and Fang Zheng Peng. "Multilevel Inverters: A survey of topologies, controls and applications." IEEE Trans. Ind.Electronics.vol-49 no.4 pp 724-738, Aug. 2002.

- [4]. K. Jang-Hwan, S.-K. Sul, and P. N. Enjeti, "A carrierbased PWM method with optimal switching sequence for a multilevel four-leg voltage source inverter," IEEE Trans. Ind. Appl., vol. 44, no. 4, pp. 1239–1248, Jul./Aug. 2008.

- [5]. Nabe, I. Takahashi and H. Akagi. "A new neutral point clamped PWM inverter." IEEE Trans. Ind. Applicat. Vol. 1A-17, pp 518- 523, sep. /oct. 1981.

- [6]. E.Najafi, A.H.M.Yatim and A.S. Samosir. "A new topology-reversing voltage (RV) for multi-level inverters." 2nd International conference on power and energy (PECon 08), pp 604-608, December 2008 Malaysia.

- [7]. Ehsan Najafi, and Abdul Halim Mohamed Yatim, "Design and Implementation of a New Multilevel Inverter Topology," IEEE Transactions on industrial electronics, vol. 59, no. 11, November 2012.

- [8]. Jacob James Nedumgatt, Vijayakumar D., A. Kirubakaran, Umashankar S. "A Multilevel Inverter with Reduced Number ofswitch Switches," IEEE Students' Conference on Electrical, Electronics and Computer Science 2012.

- [9]. Napaphat Lekgamheng and Yuttana Kumsuwan "Phase-Shifted PWM Stretegy of a Seven-level Single-Phase Current Source Inverter For Grid-Connectio Systems," IEEE Trans. Ind. Appl. vol. 978-1-4673-1792-4/13 2013.

#### BIOGRAPHIES

Aditya parashar Scholar at MITS Gwalior, MP, INDIA

E-mail: adi.18ja Prof. Praveen Bansal

Prof at MITS gwalior Scholar at MITS Gwalior, MP, INDIA E-mail: Pbansal444@gmail.com n@gmail.com