# MODELLING OF NEXT ZEN MEMORY CELL USING LOW POWER **CONSUMING HIGH SPEED NANO DEVICES**

Jayanta Gope<sup>1</sup>, Sanjay Bhadra<sup>2</sup>, Gangesh Gulshan<sup>3</sup>, Kumar Sanni Sinha<sup>4</sup>

<sup>1</sup>A.P, ECE Dept., Camellia School of Engg and Tech., West Bengal, India <sup>2</sup>A.P, EE Dept., Camellia School of Engg and Tech., West Bengal, India <sup>3</sup>Student, EEE Dept, Camellia School of Engg and Tech., West Bengal, India <sup>4</sup>Student, EEE Dept, Camellia School of Engg and Tech., West Bengal, India

# Abstract

Hybrid SET-CMOS circuits which syndicate the assets of both the SET [Single Electron Transistor] and CMOS depicts highest possibilities to be incorporated in practical implementation for future low power VLSI/ULSI configurations. The proposed work is an attempt based on SET-CMOS hybrid circuit to realize the next gen simple Memory Cell. The authors adhered to MIB model for SET and BSIM4 model for CMOS in realizing the complex cell. The maneuver of the proposed circuit is verified subsequently in standard environment. The outcomes are in good trade off with the conventional statistics of existing memory cell.

\_\_\_\_\_\_\*\*\*\_\_\_\_\_\_\_

Keywords: SET, SED, Hybrid CMOS-SET, MIB and Memory Cell

# **1. INTRODUCTION**

The 2003 edition of the International Technology Roadmap for Semiconductors forecasts the pathway of ultra-thin body (UTB) CMOS transistors by 2015; the possible miniaturization is to reach gate lengths within 10 nm. This in fact renders that today's device speed has enhanced by four orders of magnitude from the earlier device speed [1 & 2]. It gives the impression that the device scaling down trend of CMOS transistors is likely to endure its exponential growth for the next few couple of decades. Contrariwise, Moore's prediction of device down scaling by no means is a never-ending process. The penalties of technological limitation on CMOS technology immensely distress the trimming of CMOS transistors. Researchers reported several empirical studies based technological limitations owing to physical laws, application limits and the manufacturing limitations [3 & 4]. Such has endangered the end of CMOS technology possibly within this decade; thus the requisite for a successor is now foreseeable.

Then after the exploration of possible successor technologies with greater scaling potential attracted Researchers. Few new invented technologies are Rapid Single Flux Quantum (RSFQ), Resonant Tunneling Diodes (RTD), Single Electron Device (SED), Carbon Nano-tubes and Magnetic Spin devices [5 - 14] and reports revealed that they are quite impressive in post CMOS era. Manipulation of a single charge of electron through tunneling is the ultimate point of operation in device electronics. This is a major research boom for the last two decades and also produced several new technologies. This attributes electron transport metaphor in confined structure in nano regime. The Single Electron Tunneling (SET) technology has created high expectations for post CMOS era as it is compatible for designing low power consuming nano-scaled device that posses high integration density [15 - 18]. The development made so far in SET technology is divided in: -(i) Device Research which consist of device fabrication and fabrication technology studies. Scientists all over the world have devoted largely in this category; and (ii) The Application of SET devices for various purposes is a different and completely new aspect to explore but only a little has been achieved in this category. In present context, authors are emphasizing in realizing fast switching, low power and less space consuming SET based memory cell to substitute the conventional CMOS memory cell as SET appears better candidate for the survival of the fittest in modern electronics [19 - 22].

# 1.1 Diagnostic Study of Set

Describing SET is quite similar to a small conductor, which is at the outset an 'electro neutral', having exactly as many electrons as it has protons in its crystal lattice. In this form any significant electric field is not generated by the island afar its border. Predominantly an additional electron may propel in due to a weak external force. Now the net charge is  $e^{-}$ . Here the charging energy of the island is denoted by  $E_{C}$ , where the total capacitance is C and  $E_C$  can be calculated as [23 & 24]

$$E_{c=}\frac{e^2}{c}$$

Most interestingly only if the size of the island becomes equivalent with the de Broglie wavelength of the electron inside the island, the energy quantization

$$E_{N=} \frac{(n\pi\hbar^2)}{2xw^2} + \frac{\hbar^2k^2}{2x}$$

$$E_a = E_C + E_K$$

$$E_K = \frac{1}{g(\in_F)V}$$

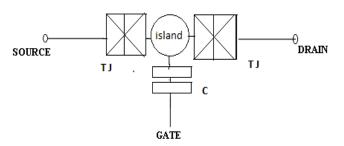

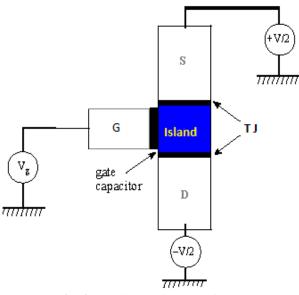

The most promising applications for SETs are (i) chargesensing applications such as the readout of few electron memories, (ii) the readout of charge –coupled devices and (iii) precision charge measurement in metrology. Beneath here the authors have included the general architecture of SET in Fig 1 and 2.

Fig -1: Simple SET structure

Fig -2: Detailed realization of SET

#### 1.2 Need of Hybridization

Detailed research in SET has attracted attention as a candidate for future VLSI circuits owing to its three features: nano scale feature size, ultralow power dissipation, and unique Coulomb blockade oscillation features. Amid such overwhelming properties, the practical execution of the SET is under scanner because of its low current drive and lack of mature room temperature operable technology. SET advocates low power consumption and new functionality (related to the Coulomb blockade oscillations), while CMOS has advantages such as high-speed driving and voltage gain that can compensate for the intrinsic drawbacks of SET. Though a complete replacement of CMOS by SET is not easy task to achieve but simultaneously it is also true that the combination of SET and CMOS can bring a new era in VLSI technology [25 -28].

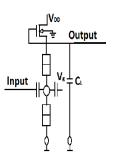

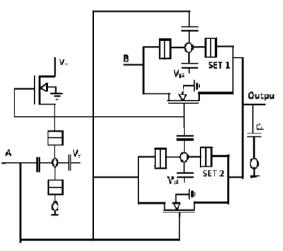

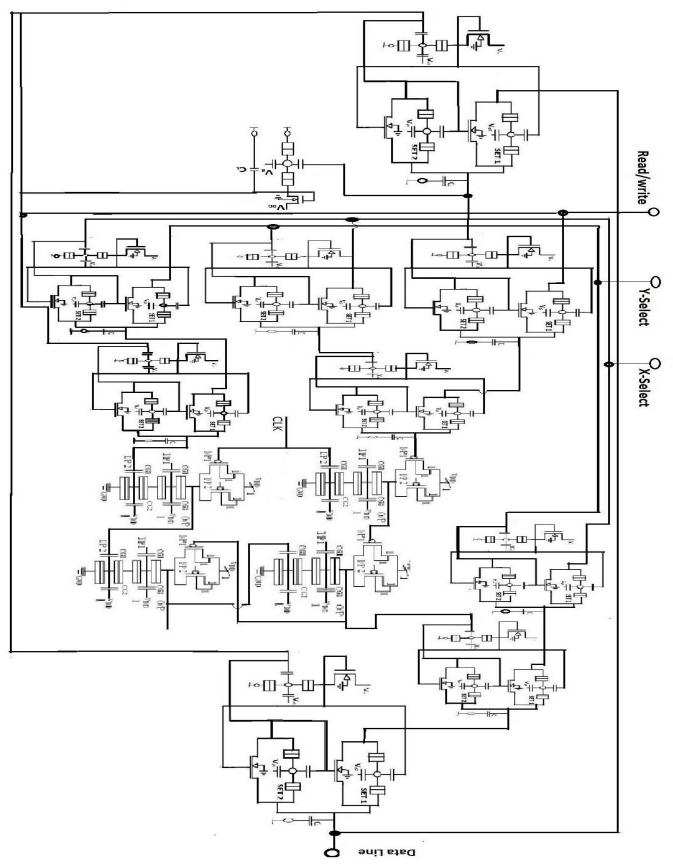

Researchers at Delft University in Netherlands endorsed a SPICE simulation package for SET circuit [29] employing Orthodox theory of SET. The authors here follow the SET-MOS quaternary transmission gate [30] which is highly accredited and mostly cited in reputed journals. The cointegration model of Parallel-In-Serial-Out Shift Register were designed and further simulated on this above cited SPICE soft-computing layout which allows place sharing of SETs with the conventional MOS devices in one particular die area as elucidated in Fig. 3. More conveniently, the logic operations of the proposed circuit were first tested by simulation using T-Spice simulation software. Thereafter, MIB compact model for SET device and BSIM4.6.1 model for CMOS was incorporated for obtaining detailed empirical results which are briefly included in this presentation. Following are some realizations of Hybrid CMOS-SET based logic devices:

Fig -3: Hybrid CMOS-SET based simple Inverter

Fig -4: Hybrid CMOS-SET based simple AND logic implementation

Fig -5: Hybrid CMOS-SET based simple OR logic implementation

# 2. BASIC MEMORY CELL

## CONCEPTUALIZATION

The memory cell is well defined as the fundamental building block of memory, usually implemented using bipolar, MOS, and other semiconductor devices or from magnetic material like ferrite cores or magnetic bubbles. Notwithstanding any of the implementation technology, the purpose of the binary memory cell remains identical as it stores one bit of binary information at particular time span and it must be set to store a 1 and reset to store a 0. Memory is a key element of digital systems and is also employed in designing temporary storage of the output of combinational circuits - thereby creating sequential circuits. Its output solely depends not merely on the present value of its inputs, rather on the circuit's previous state. Orthodox theory on memory cells are reported several times in SCI journals [31-33]. The incorporation of memory cells are thereby very common in today's computer kernels.

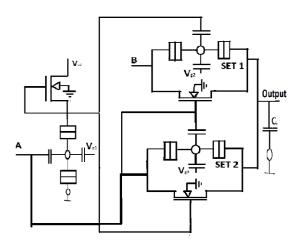

#### 2.1 Proposed Hybrid CMOS SET based Memory

#### Cell

The authors refer here the proposed model enumerated in Fig. 6. This cell comprises of low power consuming hybrid CMOS SET based R-S flip-flop and the inputs are controlled by hybrid CMOS SET based 4-input AND gates. In order to perform the desirable read/write operation on this cell, the control points is made high i.e., 1. Here logic 1 is made by giving input voltage @ 0.8mV and the logic 0 is provided by making the input voltage equal to 0mV. Thus the circuit can operate in very low voltage. More conveniently the hybrid CMOS-SET based memory cell is extremely low power consuming device.

#### 2.1.1 Write Operation

For writing data into this memory cell, the authors ponder over the following control signals.

X-select = 1

Y-select = 1

$\overline{RD}_{/WR} = 1$

Under these signal conditions, the first three AND gates (starting from the left) and the AND gate just beyond the flip-flop are enabled while AND gate that drives the output is disabled. Data present on the data line is therefore transferred through three AND gates and are loaded into the flip-flop.

# 2.1.2 Read Operation

For read operation, the memory cell has to perform in the following manoeuvre

$\begin{array}{l} \text{X-select} = 1\\ \text{Y-select} = 1 \end{array}$

$$\overline{RD}_{/WR} = 0$$

X-select and Y-select signals enable two AND gates in the

middle section of the proposed model, but the  $RD_{/WR}$  remains 0 i.e., it is disabled. Then after again the first three AND gates are periodically enabled and simultaneously the same occurs for the last output driving AND gate. this ensures that the consecutive last two AND gates remain enabled and output becomes available on the date line.

#### **3. CONCLUSION**

The design and simulation of hybrid CMOS-SET basic memory cell is modelled successfully and the results are obtained categorically to expose the underlying potential of perfect co-integration of CMOS-SET. One remarkable attribute is that the SET and CMOS are placed in series and thereby the hybridization achieved improves the gain of the models and simultaneously the propagation delay is lessened to some extent. Based on the hybrid CMOS-SET logic gates, the model was designed and implemented using sophisticated simulation software.

# REFERENCES

- [1] Subir Kumar Sarkar, "VLSI BEYOND CMOS DEVICES: NANO, SINGLE ELECTRON AND SPINTRONIC DEVICES", IET-UK International Conference on Information and Communication Technology in Electrical Sciences (ICTES 2007), Dr. M.G.R. University, Chennai, Tamil Nadu, India. Dec. 20-22, 2007. pp. 1-7.

- [2] P.K Sahu, A. K.Biswas and Subir Kumar Sarkar, "Realization of fast switching, low power and les space consuming logic circuits using single electron devices: A case study" International Journal of Information and Computing Sciences. Vol.7. No. 1, pp 54, 2004.

- [3] D. Bhattarya, P. Agrawal, and V. D. Agrawal: Proc. Design Automation Conference (DAC), Aaheim CA, 159 (1992).

- [4] A. K. Biswas, Samir Kumar Sarkar and Subir Kumar Sarkar, Int. Journal of Information and Computing Science, vol. 5, No.2, 2003.

- [5] N.Asahi et al.: "BDD devices" IEEE Trans. ED '42 11, pp1999- 2003.1995.

- [6] Oya T., Asai T., Fukui T., and Amemiya Y., "Reaction-diffusion systems consisting of singleelectron circuits," International Journal of Unconventional Computing, vol. 1, no. 2, pp. 177-194, (2005).

- [7] Oya T., Schmid A., Asai T., Leblebici Y., and Amemiya Y., "Single electron circuit for inhibitory spiking neural network with fault-tolerant architecture," IEEE International Symposium on Circuits and Systems, Kobe, Japan (May 23-26, 2005)

- [8] M. A. Kastner, "The single-electron transistor," Rev. Modern Physics, vol. 64, pp. 849–858, 1992.

- [9] K. Likharev, "Quantum electronic devices for future digital systems," Future Electron Devices (FED) J., Jan. 1995.

- [10] U. Meirav and E. Foxman, "Single-electron phenomena in semiconductors," Semiconductor Sci. Technol., pp. 255–284, 1995

- [11] Mukhanov, O.A., "Rapid single flux quantum (RSFQ) shift register family", IEEE Transactions on Applied Superconductivity, 1993, Vol. 3, Issue 1, pp 2578 - 2581

- [12] R. Notzel et al., "Self-organized growth of quantumdot structures," Solid-State Electron., vol. 40, pp. 777–783.

- [13] K.P. Hirvi, J.P. Kauppinen, A.N. Korotkov, M.A. Paalanen, and J.P. Pekola, "Arrays of normal tunnel junctions in weak Coulomb blockade regime", Appl. Phys. Lett., vol. 67, pp.2096-2098,

- [14] K.K. Likharev, "Correlated discrete transfer of single electrons in ultra small tunnel junctions", IBM J. Res. Devel., vol. 32, pp. 144-158, January 1988.

- [15] Xiaobin Ou; Nan-Jian Wu, "Analog-digital and digital-analog converters using single-electron and MOS transistors" IEEE Transactions on Nanotechnology, Vol. 4, Issue: 6, 2005, pp 722 – 729.

- [16] Gang Wu, Li Cai, Qiang Kang, Sen Wang, Qin Li, "A 8-bit parity code generator based on multigate single electron transistor" 3rd IEEE International Conference on Nano/Micro Engineered and Molecular Systems, 2008. NEMS 2008.

- [17] Wan-cheng Zhang, Nan-jian Wu, Hashizume, T., Kasai, S, "Multiple-Valued Logic Gates Using Asymmetric Single-Electron Transistors" 39th International Symposium on Multiple-Valued Logic, 2009. ISMVL '09. IEEE, pp 337 – 342.

- [18] Xavier Jehl and Marc Sanquer, "Progress on Single-Electron Transistors" ICICDT-10, 2010 IEEE

- [19] Subir Kumar Sarkar, Samir Kumar Sarkar, Jayanta Gope, Tarun Kumar Chatterjee, Senthil Kumar and Gautam .M.A "Single Electron Device Based Application Specific Integrated Circuit Design for Use in Stock Market" In National Conference on Advanced Computing and Computer Networks

(NCACCN 2007), Vikhe Patil College of Engineering, Ahmednagar, Maharasthtra on 9-10 March 2007.

- [20] Subir Kumar Sarkar, D. Samanta, S. Sarkar, K. Senthil Kumar, J. Gope and Ankush Ghosh, "Single electron device based string detector for the identification of Frame Delimiters in Data Transfer Protocols", National Conference on Digital Information Management (NCDIM'07), Thadomal Shahani Engineering College & Computer society of India, Mumbai-400050, during 23-24th March 2007.

- [21] C. J. Clement Singh, K Senthil Kumar, Jayanta Gope, Suman Basu, and Subir Kumar Sarkar "Single Electron Device Based Tea Vending Machine", International Engineering and Technology (IETECH) Journal of Information Systems, Vol-2; No:2, 2008, pp 046-051.

- [22] Jayanta Gope, Giriprakash H, Subir Kumar Sarkar, "Cellular Automata Based Data Security Scheme in Computer Network using Single Electron Device" Special Issue of IJCCT Vol.1 Issue 2, 3, 4; 2010 for International Conference [ACCTA-2010], 3-5 August 2010

- [23] Xavier Jehl and Marc Sanquer, "Progress on Single-Electron Transistors" ICICDT-10, 2010 IEEE

- [24] S.K. Sarkar et al..; in the proceedings of 2nd People's Technology congress held in Feb 3-5 of 1999, at Science City, Calcutta.

- [25] Santanu Mahapatra and Adrian Mihai Ionescu "Realization of multiple valued logic and memory by hybrid SETMOS architecture" IEEE transactions on Nanotechnology, Vol. 4, No. 6, November 2005.

- [26] Kevin Ovens, Clive Bittlestone, Bob Helmick "Transmission Gate Circuit" – Texas Instruments Incorporated, Dallas, Tex.

- [27] Linfeng Li and Jianping Hu "A Transmission Gate Flip-flop Based on Dual Threshold CMOS Technique" – 52nd IEEE International Midwest Symposium on Circuits and Systems, 2009.

- [28] G.Lientsching, I.Weymann and P.Hadley "Simulating Hybrid Circuits of Single Electron Transistors and Field Effect Transistors" – Japanese Journal of Applied Physics, vol. 42, pp 6467 – 6472, 2003.

- [29] S. Mahapatra, A.M. lonescu, K. Banejee, M.J.Declerq, "Modelling and analysis of power dissipation in single electron logic", Technical Digest of IEDM 2002.

- [30] K. Uchida, 1. Koga, R. Ohba, A. Toriumi, "Programmable single-electron transistor logic for low-power intelligent Si LSI", ISSCC 2002, Vol. 2, pp. 162453.

- [31] Fletcher, William (1980). An engineering approach to digital design. Prentice-Hall. p. 283. ISBN 0-13-277699-5.

- [32] Microelectronic Circuits (Second ed.). Holt, Rinehart and Winston, Inc. 1987. p. 883. ISBN 0-03-007328-6.

- [33] "La Question Technique: le cache, comment ça marche ?". PC World Fr

#### BIOGRAPHIES

Dr. Jayanta Gope, PhD (Engg.), & Chartered Engineer has received his PhD Degree in Nanotechnology from Jadavpur University, Kolkata and is presently associated with Camellia School of Engineering and Technology. His field of interest includes Nano device modeling, Single Electronic

devices, Spintronic Devices, Hybrid CMOS-SET. He has already published around 40 International research articles in this category. He is nominated as Editorial Board Member and Reviewer of some esteemed Journals and is guiding 4 PhD Scholars in the field of Nanotechnology. He is a life Member of 'CE'& 'ISCA'.

Mr. Sanjay Bhadra, (M.E-Elect Control-JU),MBA(IT-JU) MIE,MIETE is presently associated as Asst.Prof(EE) in Camellia School of Engineering and Technology. He has active interest in Signal processing and nano devices. Presently he is pursuing PhD in nano

device engineering.

Mr. Gangesh Gulshan is a final year student of B.Tech in Electrical and Electronics Engineering Department of Camellia School of Engineering and Technology, West Bengal, India.

Mr. Kumar Sanni Sinha is a final year student of B.Tech in Electrical and Electronics Engineering Department of Camellia School of Engineering and Technology, West Bengal, India.

Fig -6: Hybrid CMOS-SET based Memory Cell