# A NOVEL SINGLE-PHASE CASCADED H-BRIDGE INVERTER WITH NEW CELL CONFIGURATION AND REDUCED POWER ELECTRONICS COMPONENTS WITH LOW THD

# Arun kumar.M<sup>1</sup>, Kaliamoorthy.M<sup>2</sup>, Brindha.P<sup>3</sup>, Rajasekaran.V<sup>4</sup>, Chandrasekaran.N<sup>5</sup>

<sup>1</sup>PG Scholar, Department of Electrical and Electronics Engineering, PSNA CET, Tamilnadu, India <sup>2</sup>Associate Professor, Department of Electrical and Electronics Engineering, PSNA CET, Tamilnadu, India <sup>3</sup>PG Scholar, Department of Electrical and Electronics Engineering, PSNA CET, Tamilnadu, India <sup>4</sup>Professor, Department of Electrical and Electronics Engineering, PSNA CET, Tamilnadu, India <sup>5</sup>Professor, Department of Electrical and Electronics Engineering, PSNA CET, Tamilnadu, India

#### **Abstract**

This project presents Single-phase Cascaded H-Bridge Inverter with minimum number of power electronics devices. The proposed Inverter consists of 4 unidirectional switches and single bidirectional switch in each cell. Single carrier and Multicarrier PWM method is used to generate the multilevel output. The proposed multilevel Inverter is compared with conventional symmetrical CHB, Asymmetrical CHB with binary and trinary configurations. The comparison will be made on the basis of number of components, number of DC sources, number of Balancing capacitors, Switching and conduction losses. The proposed Cascaded H-Bridge Inverter will be simulated using MATLAB/SIMULINK and will be implemented in hardware also using SPARTAN3A DSP.

Keywords - Bi-directional Switches, Cascaded H-bridge Inverter, DC to DC Boost Converter, Multi carrier PWM, PV array

\_\_\_\_\_\*\*\*\_\_\_\_\_

#### 1. INTRODUCTION

Over the past few years, technological advances in power electronics and increasing demand for energy have contributed to rapid development of power generation based on renewable energy sources as like the Photovoltaic (PV), Wind and Fuel cell (FC) based renewable energy technologies [3].

One of the problems focused in the research is the constraint of power electronic switches. If the power electronic devices which can prolong high voltage are used in the inverter, their switching frequency is restricted. Hence, the device voltage must be reduced to use high-speed switching devices. A multilevel inverter can reduce the device voltage and the output harmonics by increasing the number of output voltage levels. Further, increase in number of isolated DC sources in order to increase the number of output voltage levels leads to additional system complexity especially in PV and FC fed inverter topologies. In single-phase multi-level inverters, the most widely used techniques are cascaded H-bridge (CHB), diode-clamped and capacitor-clamped types [7-9]. In addition, many other techniques also exist. In particular, among these techniques, CHB single phase inverters have drawn attention because of their modularized circuit layout and simplicity. A variety of modulation techniques can be applied to CHB inverters. By increasing the number of cascaded H-bridges,

the number of levels in CHB inverters increases. Generally if the number of output voltage levels is increased, then the number of power electronic devices and the number of isolated DC sources is also increased. This makes a CHB inverter further complex.

eISSN: 2319-1163 | pISSN: 2321-7308

In this paper, a novel multilevel inverter with minimum number of power electronic switching devices is proposed which is a modified version of the multilevel inverter using series/parallel conversion of DC sources. In the proposed Multilevel Inverter three similar Cascaded H-Bridges are used, each Bridge carries an auxiliary switch which will be Bidirectional in nature. The proposed multilevel inverter topology can be extended for the application of grid connected photo voltaic systems, hybrid electric vehicles, etc. Furthermore, theoretical analysis, numerical simulations and experimental results are also presented to demonstrate the validity of the proposed single phase cascaded multilevel inverter.

Basically Inverter is a device that converts DC power to AC power at desired output voltage and frequency. Demerits of inverter are less efficiency, high cost, and high switching losses. To overcome these demerits, we are going to multilevel inverter. The term Multilevel began with the three-level converter. The concept of multilevel converters has been

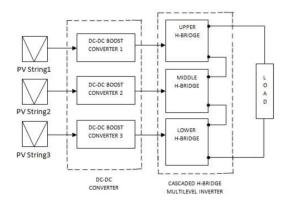

introduced since 1975 [1]. The cascade multilevel inverter was first proposed in 1975. In recent years multi level inverters are used high power and high voltage applications. Multilevel inverter output voltage produce a staircase output waveform, this waveform look like a sinusoidal waveform. The multilevel inverter output voltage having less number of harmonics compare to the conventional bipolar inverter output voltage. The multi level inverters are mainly classified as Diode clamped. Flying capacitor inverter and cascaded multi level inverter. The cascaded multilevel control method is very easy when compare to other multilevel inverter because it doesn't require any clamping diode and flying capacitor [2-3]. There are two PWM methods mainly used in multilevel inverter control strategy. One is fundamental switching frequency and another one is high switching frequency. For high switching frequency classified as space vector PWM, Selective Harmonics Elimination PWM and SPWM. Among these PWM methods SPWM is the most used for the multilevel inverter, [7]. This proposed work is implemented with another major advantage of using the supply as the Renewable energy sources (PV Cells). The output from the PV string will be very small in value hence, the output voltage can be boosted up by the use of boost converter. The boost converter is used for two purposes. (i) Boost converter acts as a DC-DC step up transformer, to boost up the voltage required to drive the inverter. (ii) Boost converters are used for balancing the input capacitor voltages. The output from the boost converter feds the power to the inverter structure which drives the load connected across its terminals. The Overall Block Diagram for the Proposed Inverter is shown in Fig 1.1.

Fig. 1.1 Overall Block Diagram

# 2. PROPOSED INVERTER CONFIGURATION

## 2.1 Introduction

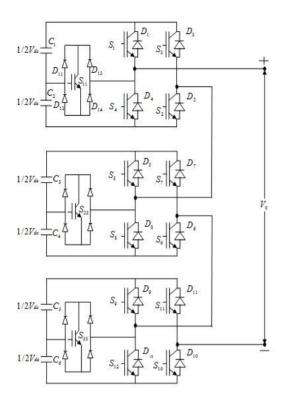

Fig 2 shows the circuit configuration of the proposed cascaded H bridge multilevel inverter with three H-Bridge inverters connected in cascade (Upper, Middle and Lower H-bridge inverters). As shown in Fig. 2, in the lower H bridge, an

auxiliary circuit comprising of four diodes and a switch is placed between two DC sources.

eISSN: 2319-1163 | pISSN: 2321-7308

This cascaded multilevel inverter made up of series connected single full bridge inverter each with their own isolated dc bus. This multilevel inverter can generate almost sinusoidal waveform voltage from several separate dc sources, which is obtained from solar photo voltaic cells. This type of converter does not need any transformer or clamping diodes or flying capacitors. Each level can generate five different voltage outputs  $+V_{\rm dc},\,+1/2v_{\rm dc},\,0$ ,  $-V_{\rm dc}$  and  $-1/2v_{\rm dc}$  by connecting the dc sources to the ac output side by different combinations of the five switches.

The output voltage of an M-level inverter is the sum of all the individual inverter outputs. Further, each switching device always conducts for 180° (or half cycle). This topology of inverter is suitable for high voltage and high power inversion because of its ability of synthesize waveforms with better harmonic spectrum and low switching frequency. Considering the simplicity of the circuit and advantages, Cascaded H-bridge topology is chosen for the presented work.

# 2.2 Operation

The circuit diagram of proposed method of multilevel cascaded inverter as shown in Figure 2. It consists of three full-bridge cells, capacitor voltage divider, three auxillary switches. The inverter produces output voltage in thirteen levels:  $0.5V_{dc},\ V_{dc},\ 1.5V_{dc},\ 2V_{dc},\ 2.5V_{dc},\ 3\ V_{dc},\ 0,\ -0.5V_{dc},\ V_{dc}$ , -1.5 $V_{dc}$ , -2 $V_{dc}$ , -2.5 $V_{dc}$ , -3  $V_{dc}$ . The advantages of the inverter topology are: Improved output voltage quality, Smaller filter size, Lower Electromagnetic interferences, Lower total harmonics distortion compared with conventional fifteen level pulse width modulation with reduced number of switches compared to the conventional CHB inverter. The Additional component added here is the Bi-Directional Switch. By defenition a Bi-Directional switch in literature also named Bilateral switch or AC switch or 40 Switch(O Stands for Quadrant) capable of conducting currents and blocking voltages of both polarities, depending on control actual signal.

Fig. 2.1 Cell Configuration for the Proposed Inverter

The cascaded H-bridges multilevel inverter introduces the idea of using separate dc sources to produce an ac voltage waveform. Each H-bridge inverter is connected to two capacitors 0.5Vdc. By cascading the ac outputs of each H bridge inverter, ac voltage waveform is produced. By closing the appropriate switches, The system consists of 15 switches which can be used to produce those thirteen different output voltage levels such as,  $\bar{0}$ , 0.5  $V_{dc}$ , 1  $V_{dc}$ , 1.5  $V_{dc}$ , 2  $V_{dc}$ , 2.5  $\bar{V}_{dc}$ 3  $V_{dc}$ , -0.5  $V_{dc}$ , -1  $V_{dc}$ , -1.5  $V_{dc}$ , -2  $V_{dc}$ , -2.5  $V_{dc}$ , -3  $V_{dc}$ . The switching strategy for various output voltages in the proposed 3 cell configuration is clearly shown in Table I.

When a switch S2 and S4 of one particular H-bridge inverter are closed, the output voltage is 0. When a switch S2, A5, are closed, the output voltage is +0.5V<sub>dc</sub>. When a switch S1, S2, S6, S8, S10, S12 are closed, the output voltage is  $+V_{dc}$ . When a switch A1, S2, S5, S6, S10, S12 of one particular H-bridge inverter are closed, the output voltage is +1.5V<sub>dc</sub>. When a switch S1, S2, S5, S6, S10, S12 are closed, the output voltage is +2V<sub>dc</sub>. When a switch S1, S2, S5, S6, A3, S10 are closed, the output voltage is  $+2.5V_{dc}$ . When a switch S1, S2, S5, S6, S9, S10 are closed, the output voltage is  $+3V_{dc}$ . Similarly for the negative voltages the switching sequences appears. Therefore totally, thirteen levels of output voltage appears on the load side.

Many kind of inverters are available in the various configurations with a desired level ofoutput voltages.

Those various inveters are compared under the various components and switches.

Table -1: Thirteen-level Cascaded H-Bridge inverter output voltage.

|                   | 1                  |                   | 1                          |

|-------------------|--------------------|-------------------|----------------------------|

| UPPER<br>INVERTER | MIDDLE<br>INVERTER | LOWER<br>INVERTER | TOTAL<br>OUTPUT<br>VOLTAGE |

| S1,S2             | S5,S6              | S9,S10            | $3V_{dc}$                  |

| S1,S2             | A2,S6              | S9,S10            | $2.5V_{dc}$                |

| S1,S3             | S5,S6              | S9,S10            | $2V_{dc}$                  |

| A1,S2             | S5,S7              | S9,S10            | $1.5V_{dc}$                |

| S1,S3             | S5,S7              | S9,S10            | $V_{dc}$                   |

| A1,S2             | S6,S8              | S10,S12           | $0.5V_{dc}$                |

| S1,S3             | S5,S7              | S9,S11            | 0                          |

| S1,S3             | A2,S7              | S9,S11            | -0.5V <sub>dc</sub>        |

| S2,S4             | S6,S8              | S11,S12           | -V <sub>dc</sub>           |

|                   |                    |                   |                            |

| A1,S3             | S6,S8              | S11,S12           | $-1.5V_{dc}$               |

| S1,S3             | S7,S8              | S11,S12           | -2V <sub>dc</sub>          |

| ,,                |                    | ,,,,,             | uc uc                      |

| S3,S4             | A2,S7              | S11,S12           | -2.5V <sub>dc</sub>        |

|                   |                    |                   |                            |

| S3,S4             | S7,S8              | S11,S12           | -3V <sub>dc</sub>          |

|                   |                    |                   |                            |

## 2.3 Comparison between Different Topologies

The proposed topology is compared with conventional symmetrical CHB inverters, asymmetrical CHB inverter with 1:3 configuration, asymmetrical CHB inverter with 1:2:4 configuration and asymmetrical CHB inverter with 1:3:9 configuration. The comparison is done on the basis of number of components and rating of the devices [8].

As per the comparison, In the symmetrical CHB - to produce a 5 level output, eight switches are required in the ratio of 1:1 configuration. Similarly for a 7 level output, same eight switches are required in the ratio of 1:1:1 configuration. Further, to increase the levels the voltage ratios must be increased,  $V_{dcn}/V_{dco = n}$ , that depends upon the number of output voltage level required.

## 3. PWM MODULATION STRATEGY

The modulation index M of the proposed multilevel inverter is defined by

$$M = \frac{1}{2} \frac{V_{ref}}{V_{cr}} \tag{1}$$

Where,  $V_{\text{ref}}$  is the amplitude of the voltage reference and  $V_{\text{cr}}$ is the amplitude of the carrier signal.

Multicarrier phase-shifted PWM (CPS-PWM) modulation is used to generate the PWM signals. The amplitude and frequency of all triangular carriers are the same as well as the phase shifts between adjacent carriers. Depending on the number of cells, the carrier phase shift for each cell  $\theta Cr, n$  can be obtained from.

Table -2: Component Level Comparison.

| S.No | TYPE OF INVERTER | Primary Devices             | OUTPU<br>T |  |

|------|------------------|-----------------------------|------------|--|

|      |                  |                             | LEVEL      |  |

| 1    | Diode            | $PD_{11}=20$ for 13         | N=13       |  |

|      | Clamped          | levels                      |            |  |

|      | Multi-level      | $PD_{N}=PD_{(N-4)}+3$       |            |  |

|      | Inverter         | Where N=levels              |            |  |

| 2    | MLISPC           | PD <sub>11</sub> =16 for 13 | N=13       |  |

|      |                  | levels                      |            |  |

|      |                  | $PD_{N}=PD_{(N-4)}+3$       |            |  |

|      |                  | Where N=levels              |            |  |

| 3    | Conventional     | PD <sub>11</sub> =16 for 13 | N=13       |  |

|      | CHB              | levels                      |            |  |

|      |                  | $PD_{N}=PD_{(N-4)}+4$       |            |  |

|      |                  | Where N=levels              |            |  |

| 4.   | Proposed         | PD <sub>11</sub> =15 for 13 | N=13       |  |

|      | Inverter         | levels                      |            |  |

|      |                  |                             |            |  |

|      |                  |                             |            |  |

$$\theta_{cr,n} = \frac{2\pi(n-1)}{N_c}, n = 1, 2, \dots, n_c$$

(2)

The references, vref1 and vref2 are derived from a full-wave voltage reference, Vref defined by

$$V_{ref} = M \sin \omega t \tag{3}$$

$$V_{ref1} = |V_{ref}| \tag{4}$$

$$V_{ref 2} = V_{ref 1} - \frac{1}{2} \tag{5}$$

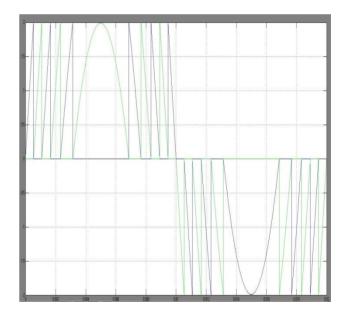

Both references are identical but displaced by an offset equal to the carrier's amplitude which is 1/2. When the voltage reference is between  $0 < v_{\text{ref}} \le (1/2)$ ,  $v_{\text{ref1}}$  is compared with the triangular carrier and alternately switches S1 and S3 while maintaining S5 in the ON state to produce either  $(1/2)v_{\rm dc}$  or 0. Whereas, when the reference is between  $(1/2) < v_{ref} \le 1$ ,  $v_{ref2}$  is used and alternately switches S1 and S2 while maintaining S5

n the ON state to produce either  $(1/2)v_{\rm dc}$  or  $v_{\rm dc}$ . As for the reference between  $-(1/2) < v_{ref} \le 0$ , vref1 is used for comparison which alternately switches S1 and S2 while maintaining S4 in the ON state to produce either  $-(1/2)v_{dc}$  or 0. For a voltage reference between  $-1 < v_{ref} \le -(1/2)$ ,  $v_{ref2}$  is compared with the carrier to produce either  $-(1/2)v_{dc}$  or  $-v_{dc}$ alternately switches S1 and S3, maintaining S4 in the ON state. It is noted that two switches, S4 and S5, only operate in each reference half cycle. This implies that both switches operate at the fundamental frequency while the others operate close to the carrier frequency.

The various output voltage for the each cells (ie., Upper, Middle, Lower) is obtained. And the combination of these voltage levels is the total output voltage for the proposed Inverter.

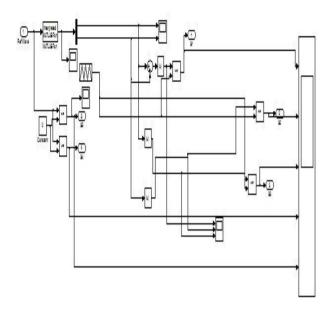

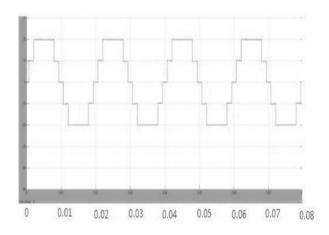

The separate reference waves are developed by using a Interpreted MATLAB function, and hence the developed signal is shown in Fig. 3.1. and Similarly for the Middle and Lower level Bridges in Fig. 3.2 and Fig. 3.3.

The Generated Gate pulses are fed to the relevant Inveter Bridges and hence the desired output for each and every bridge is obtained, the number of output levels generated are combined to get the actual number (ie., thirteen level output) of output levels are generated.

Fig 3.1 Reference Wave Signal Generation for the Upper Bridge Inverter

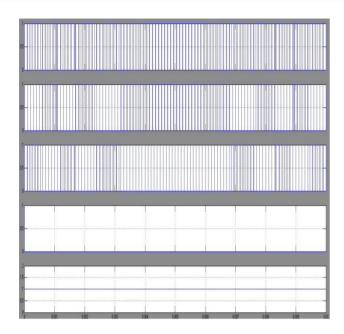

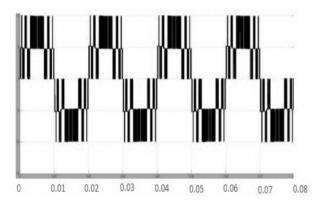

Fig 3.2 Generated Gate Pulses for Upper Bridge Switches

Fig 3.3 Generated Gate Pulses for Middle and Lower Bridge Switches

#### 4. SIMULATION RESULTS

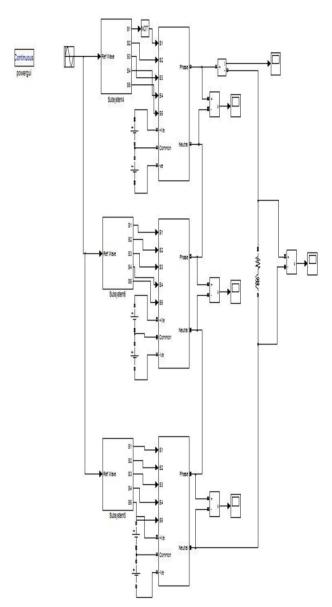

The Above Cascaded Multi-level Inverter is simulated by using MATLAB/SIMULINK software tools for generating the 13 Level output voltage.

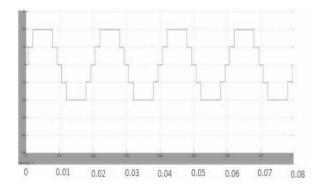

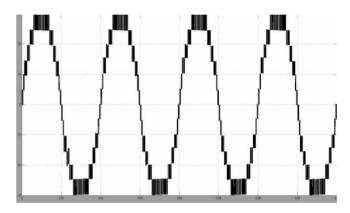

This simulation is carried out for each cells in the proposed Inverter and the combined result is taken as the total output voltage. To validate the proposed inverter topology simulation has been carried out for the proposed inverter in Matlab/Simulink. The PWM modulation strategy discussed in section III was implemented in the simulation upto 13 levels and the same can be extended to any required level. Table I gives the different switching strategies for each and every cells in the proposed inverter. The upper inverter is operated at high switching frequency that is equivalent to the carrier frequency. The output voltages for the each cells are shown in Fig. 4.3.

eISSN: 2319-1163 | pISSN: 2321-7308

**Fig 4.1** MATLAB/SIMULATION Diagram- Proposed Cascaded H-Bridge Multi-Level Inverter

**Fig 4.2** Reference Wave Signal Generation for the Upper Bridge Inverter

Fig 4.3 Generated output Waveform for the Upper Bridge

Inverter

Fig 4.4 Generated output Waveform for the Middle Bridge Inverter.

**Fig 4.5** Generated output Waveform for the Lower Bridge Inverter.

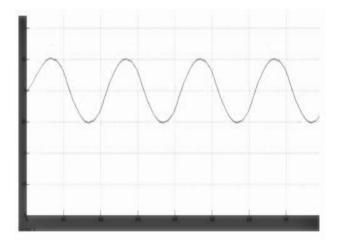

Fig 4.6 Total Output Voltage for the Proposed Cascaded H-Bridge Inverter

**Fig 4.7** Output Current Waveform for the Proposed Cascaded H-Bridge Inverter

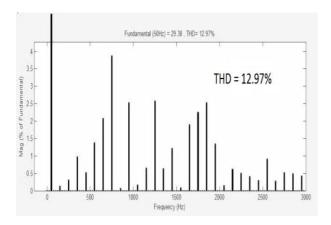

Fig 4.8 Line Voltage Harmonics with THD value

#### 5. CONCLUSIONS

This paper has presents a novel single phase cascaded Hbridge Inverter with reduced number of power electronics devices and isolated DC sources. Simulations are carried out in MATLAB/Simulink. A Generalized switching algorithm which can be used for any number of levels is presented. The performance of the suggested novel cascaded H-Bridge multilevel inverter is investigated in detail. The modulation waveform and the harmonic analysis are also presented for various values of modulation strategies. By properly adjusting the modulation index, the required number of levels of the inverter output voltage can be achieved. This proposed inverter system offers the advantage of reduced switching devices and isolated DC sources when compared to the conventional CHB and MLISPC for the same number of output levels. Also, high frequency switching devices are operated at low voltage and low frequency devices are operated at high voltage. Thus it can be concluded that the proposed novel Cascaded H-Bridge Multilevel inverter can be used for medium and high power applications. The simulation results will be verified experimentally using SPATRAN3A DSP.

#### REFERENCES

- [1] Elena Villanueva, Pablo Correa, Member, IEEE, José Rodríguez, Senior Member, IEEE, and Mario Pacas, Senior Member, IEEE "Control of a Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-Connected Photovoltaic Systems" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 56, NO. 11, NOVEMBER 2009.

- [2] Jeyraj Selvaraj and Nasrudin A. Rahim, Senior Member, IEEE "Multilevel Inverter For Grid-Connected PV System Employing Digital PI Controller" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 56, NO. 1, JANUARY 2009.

- [3] Nasrudin A. Rahim, Senior Member, IEEE, and Jeyraj

Selvaraj "Multistring Five-Level Inverter With Novel PWM Control Scheme for PV Application" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 6, JUNE 2010.

eISSN: 2319-1163 | pISSN: 2321-7308

- [4] Alexander Varschavsky, Juan Dixon, Senior Member, IEEE, Mauricio Rotella, and Luis Morán, Fellow, IEEE "Cascaded Nine-Level Inverter for Hybrid-Series Active Power Filter, Using Industrial Controller" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 8, AUGUST 2010.

- [5] M. Kavitha, A. Arunkumar, N. Gokulnath, S. Arun "New Cascaded H-Bridge Multilevel Inverter Topology with Reduced Number of Switches and Sources" IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) ISSN: 2278-1676 Volume 2, Issue 6 (Sep-Oct. 2012)

- [6] Jin Wang, Member, IEEE, and Damoun Ahmadi, Student Member, IEEE "A Precise and Practical Harmonic Elimination Method for Multilevel Inverters" IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 46, NO. 2, MARCH/APRIL 2010.

- [7] Hirofumi Akagi, Fellow, IEEE, and Ryota Kondo "A Transformerless Hybrid Active Filter Using a Three-Level Pulsewidth Modulation (PWM) Converter for a Medium-Voltage Motor Drive" IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 6, JUNE 2010.

- [8] Miguel F. Escalante, Jean-Claude Vannier, and Amir Arzandé "Flying Capacitor Multilevel Inverters and DTC Motor Drive Applications" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 49, NO. 4, AUGUST 2002 809.

- [9] H. Taghizadeh and M. Tarafdar Hagh, Member, "Harmonic Elimination of Cascade Multilevel Inverters with Nonequal DC Sources Using Particle Swarm Optimization" IEEE IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 11, NOVEMBER 2010.

- [10] "Hybrid Multicell Converter: Topology and Modulation" Pablo Lezana, Member, IEEE, and Roberto Aceitón. IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 58, NO. 9, SEPTEMBER 2011.

- [11] Samir Kouro, Member, IEEE, Mariusz Malinowski, Senior Member, IEEE, K. Gopakumar, Senior Member, IEEE, Josep Pou, Member, IEEE, Leopoldo G. Franquelo, Fellow, IEEE, BinWu, Fellow, IEEE, Jose Rodriguez, Senior Member, IEEE, Marcelo A. Pérez, Member, IEEE, and Jose I. Leon, Member "Recent Advances and Industrial Application of Multilevel Converters" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 57, NO. 8, AUGUST 2010 2553

- [12] J. S. Lai and F. Z. Peng, "Multilevel Converters-A new Breed of Power Converters," IEEE Trans. Ind. Applicat., vol.32.pp. 509-517, May/June 1996.

- [13] R. H. Baker and L. H. Bannister, "Electric Power Converter," U.S. Patent 3 867 643, Feb. 1975.

- J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel [14] Inverters: Survey of Topologies, Controls, and Applications," IEEE Transactions on Industry Applications, vol. 49, no. 4, Aug. 2002, pp. 724-738.

#### **BIOGRAPHIES**

Arun Kumar.M has obtained his B.E. degree in Electrical and Electronics Engineering from Kalasalingam University, Sriviliputhur in the year 2012 and Pursuing his M.E., degree in Power Electronics and Drives Engineering from

Anna University Chennai, during the year 2012-2014. He had presented 2 papers in International Conferences and Publised a Journal. His areas of interest include Power Electronics, Control of Drives, and Electrical Machines.

Kaliamoorthy.M received his Bachelor degree in electrical and electronics engineering at Madras University, Chennai in the year 1999 and M.Tech degree in electrical drives and control from Pondicherry University, India, in 2006 and

he is a gold medalist for the academic year 2004-2006. He has one decade of teaching experience for both under graduate and post graduate students of electrical and electronics engineering discipline. He is currently working as an associate professor in PSNA College of Engineering and technology, Dindigul, Tamilnadu, India in the Depar'tment of Electrical and Electronics Engineering. His research interests include alternative energy sources, fuel cells, energy conversion, Multilevel Inverters, analysis and control, power quality and active harmonic analysis. For further details please do visit www.kaliasgoldmedal.yolasite.com.

Brindha.P has obtained her B.E degree from Bannari Amman University, Erode in the year 2011 and Pursuing her M.E., degree in Power Electronics and Drives under Anna University Chennai, in the year 2012-2014. She had presented 1

paper in International Conference and Published her paper in a Journal. Her area of Interest includes Power Electronics, Renewable Energy Systems, and Electrical Machines. She has 1.4 years of working experience as Application Developer in iNautix Technologies India pvt.,ltd.

Chandrasekaran.N has obtained his B.E. degree from Bharathiar University, in the year 1998 and M.E., degree from Anna University Chennai, in the year 2004. He has secured first rank in M.E and got gold medal. He had completed his Ph.D under

Anna University Chennai, in the year 2014. He has published 13 papers in National Conferences and 4 papers in International Conferences. He has also published 5 papers in International journals. His areas of interest include Power Electronics. Control of Drives and Renewable Energy systems. He is a life member of ISTE. He has 13 years of teaching experience. Currently he is working as an Associate Professor in the department of Electrical and Electronics Engineering at PSNA College of Engineering and technology, Dindigul, Tamil Nadu, India.

Rajasekaran.V was born in Madurai, Tamil Nadu, India in 1971. He received his BE (Electrical and Electronics Engg) in 1994, ME (Power Systems) in 1997, and PhD in 2007 from Madurai Kamarai University, Madurai, India. He is now heading the Electrical and Electronics

Department, PSNA CET, Dindigul, TamilNadu, India. He is a certified Energy auditor. His fields of interest are Power Systems, Energy, Power Quality, Power Electronics Energy etc.