# **SPEED-POWER EXPLORATION OF 2-D INTELLIGENCE NETWORK-ON-CHIP FOR MULTI-CLOCK MULTI-MICROCONTROLLER ON** 28nm FPGA (Zynq-7000) DESIGN

# Anoop Kumar Vishwakarma<sup>1</sup>, Uday Arun<sup>2</sup>

<sup>1</sup>Student (M.Tech.), ECE, ABES Engineering College Ghaziabad, UP, India <sup>2</sup>Membership, IEEE Circuit and System Society and ACM Embedded System Computing Society

#### Abstract

Today's feature-rich multimedia products require embedded system solution with complex System-on-Chip (SoC) to meet market expectations of high performance at low cost and lower energy consumption. SoCs are complex designs with multiple embedded processors, memory subsystems, and application specific peripherals. The bus arbitration and synchronization of Multi-Microcontroller System-on-Chip (MMSoC) strongly influences the area, power and performance of the entire system as it uses switching. The synchronization is generally done by multi clocking which leads to power consumption. Future MMSoC designs will need novel on-chip communication architectures that can provide scalable and reliable data transport. On-chip network architectures are believed to be the ideal solution to many of today's SoC interconnection problems. Network-on-Chip (NoC) architectures may adopt design concepts and methodologies from Multi-Processor/Multi-Microcontroller architectures. Nevertheless, silicon implementation of networks requires a different perspective, because network architectures have to deal with the advantages and limitations of the silicon fabric. These characteristics will require new methodologies for both on-chip switch designs as well as routing algorithm designs. We envision that future on-chip systems will be communication-centric, in particular, energy and performance issues in designing the Multi-Processor/Multi-Microcontroller System-on-Chip will become challenging. In our work we have designed a switch-box for MMSoC for bus synchronization.

In this paper, we explore several critical aspects in the bus synchronization of MMSoC by using the generic Multi-Microcontroller System-on-Chip architecture as the experimental platform; this paper presents both quantitative and qualitative analysis on bus synchronization for Network-on-Chip (NoC). Commonly, we synchronize data bus only as it is more important over the other buses namely address bus, control bus and status bus. But by synchronizing other buses we can improve the overall performance of the entire Multi-Microcontroller System-on-Chip. New methodologies and solutions are also proposed to achieve better performance and power balance for MMSoCs.

\*\*\*

Keywords: SoC, MMSoC, NoC.

# **1. INTRODUCTION**

Current time embedded systems are increasingly based on Multi-Processor System-on-chip (MPSoC). These MPSoCs typically contain multiple storage elements (SEs), networks (NEs), I/O components, and a number of heterogeneous programmable processors for flexible application support as well as dedicated processing elements (PEs) for achieving high performance and power goals MPSoCs have been widely used in today's high performance embedded systems, such as network processors (NP), Mobile Phones (MP) and parallel media processors (PMP). They combine the advantages of data processing parallelism of multiprocessors and the high level integration of system-on-chip (SoC). Driven by the advancement in semiconductor technology, future SoCs will continue to accelerate in system's complexity and capacity. SoCs in the next decade are expected to integrate hundreds, or even more of, processing elements (PEs) and/or storage elements (SEs) on a single chip.

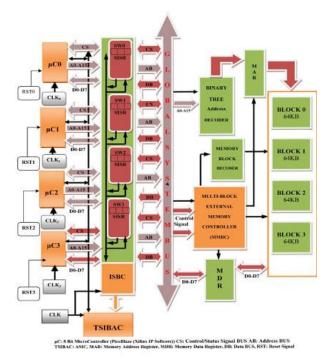

But low cost embedded systems are limited to the microcontroller performance. To improve the performance of low cost embedded system we have to develop Multi-Microcontroller System-on-Chip. So we are migrating number of low cost Microcontrollers to a single chip. To achieve it we can use the generic architecture of MMSoC (Figure 1). In generic MMSoC architecture microcontrollers are connected to the global system bus by using a switch box which is controlled by an arbitrator. To improve the performance the connected microntrollers operate parallely. As in most of cases only data bus is synchronized but by synchronizing all buses in time shared mode will improve performance and speed of MMSoC.

In order to cope with the design complexity of such systems in a time-efficient way, the abstraction level of the design process has in recent years been raised towards the system level. Design Space Exploration (DSE) is a key ingredient of such system-level design, during which a wide range of design choices are explored, especially during the early design stages. Therefore, such early design choices heavily influence the success or failure of the final product, and we can avoid wasting time and effort in further design steps without the possibility of meeting design requirements because of an inappropriate system architecture design.

Fig -1: Generic Architecture of multi-Micro Controller System-On-Chip

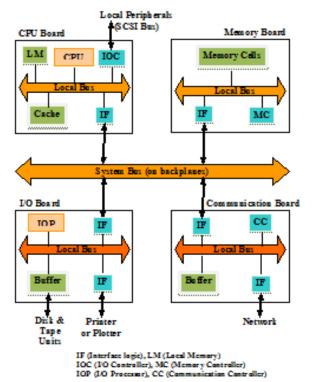

# 2. ANATOMY OF BUS SYSTEM AT BOARD,

# **BACKPLANE AND I/O LEVEL**

Fig -2: Bus system at board backplane and I/O level

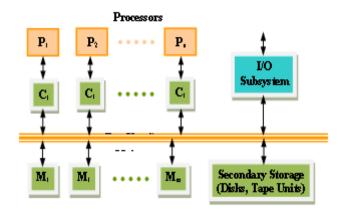

# 3. ANATOMY OF BUS-CONNECTED MULTI-PROCESSOR SYSTEM

Fig -3: A Bus-connected multiprocessor system, such as the Sequent Symmetry

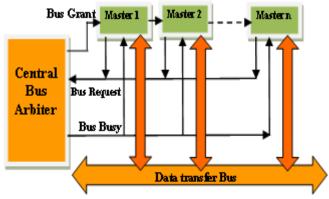

# 4. BUS ARBITRATION MODEL

Bus arbitration models are used in MPSoC/MMSoC systems. These models have only data bus is synchronized.

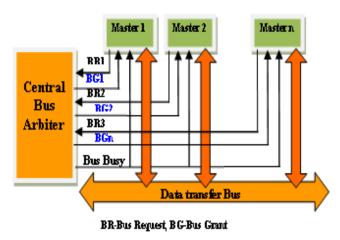

#### 4.1 Central Arbitration

Fig -4: Central Arbitration

#### 4.2 Independent Request with Central Arbiter

Fig -5: Independent Request with Central Arbiter

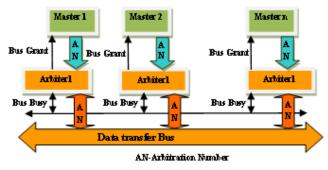

#### 4.3 Independent Request with Distributed Arbiter

Fig -6: Independent Request with Central Arbiter

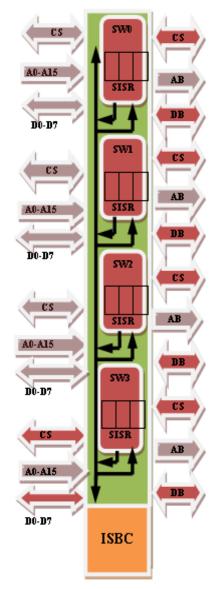

# 5. ANATOMY OF SWITCH BOX

CS-Control/Status Signal Bus, AB-Address Bus, DB-Data Bus ISBC-Intelligence Switch Box Controller SISR-Switch Box Identifier & Status Register

**Fig -7:** Anatomy of Switch Box

#### 6. RELATED WORK AND DESIGN ANALYSIS

The modeling and designing of intelligence switch box is done. The intelligence switch box shown in fig.7 has been successfully simulated and synthesized for Zynq-7000 by Xilinx Vivado 2013.4.

#### 6.1 RTL Modeling of Intelligence Switch Box

**SW00:**process(ISB\_Clk,Load\_Addr,ISBC\_ISB\_DB\_DIR,IS BC\_ISB\_CB\_DIR,ISBC\_ISB\_SB\_DIR,LSB\_AddrBus\_IN0 0,LSB\_DataBus00,LSB\_CntlBus00,LSB\_StatusBus00,ISB C\_TO\_ISB\_SBS,ISBC\_TO\_ISB\_MCID, ISBC\_TO\_ISB\_BUSID) variable SISR00 : std\_logic\_vector (2 downto 0):= "00Z"; variable ISBC\_TO\_ISB00\_MCID : std\_logic\_vector (1 downto 0):= "ZZ"; Begin

----

----

End Process

**SW01:**process(ISB\_Clk,Load\_Addr,ISBC\_ISB\_DB\_DIR,IS BC\_ISB\_CB\_DIR,ISBC\_ISB\_SB\_DIR,LSB\_AddrBus\_IN0 1,LSB\_DataBus01,LSB\_CntlBus01,LSB\_STATUSBUS01,I SBC\_TO\_ISB\_SBS,ISBC\_TO\_ISB\_MCID,ISBC\_TO\_ISB \_BUSID)

variable SISR01 : std\_logic\_vector (2 downto 0):= "00Z"; variable ISBC\_TO\_ISB01\_MCID : std\_logic\_vector (1 downto 0):= "ZZ";

begin

----

----

End Process

**SW10:**process(ISB\_Clk,Load\_Addr,ISBC\_ISB\_DB\_DIR,IS BC\_ISB\_CB\_DIR,ISBC\_ISB\_SB\_DIR,LSB\_AddrBus\_IN0 2,LSB\_DataBus02,LSB\_CntlBus02,LSB\_STATUSBUS02,I SBC\_TO\_ISB\_SBS,ISBC\_TO\_ISB\_MCID,ISBC\_TO\_ISB\_BUSID)

variable SISR10 : std\_logic\_vector (2 downto 0):= "00Z"; variable ISBC\_TO\_ISB10\_MCID : std\_logic\_vector (1 downto 0):= "ZZ";

begin

-----

End Process

SW11:process(ISB\_Clk,Load\_Addr,ISBC\_ISB\_DB\_DIR,IS BC\_ISB\_CB\_DIR,ISBC\_ISB\_SB\_DIR,LSB\_AddrBus\_IN0 3,LSB\_DataBus03,LSB\_CntlBus03,LSB\_STATUSBUS03,I SBC\_TO\_ISB\_SBS,ISBC\_TO\_ISB\_MCID,ISBC\_TO\_ISB \_BUSID)

variable SISR11 : std\_logic\_vector (2 downto 0):= "00Z"; variable ISBC\_TO\_ISB11\_MCID : std\_logic\_vector (1 downto 0):= "ZZ";

<sup>----</sup>

begin

\_\_\_\_ \_\_\_\_

\_\_\_\_

End Processs

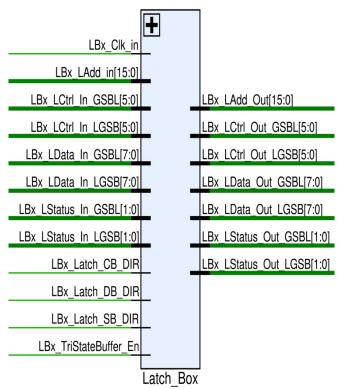

#### 6.2 RTL Modeling of Latch Box

Port ( LBx\_Clk\_in : in STD\_LOGIC; LBx TriStateBuffer En : in STD LOGIC; LBx\_LAdd\_in : in STD\_LOGIC\_VECTOR (15 downto 0); LBx\_LAdd\_Out : out STD\_LOGIC\_VECTOR (15 downto 0);

LBx\_LData\_In\_LGSB : in STD\_LOGIC\_VECTOR (7 downto 0); LBx\_LData\_Out\_LGSB : out STD\_LOGIC\_VECTOR (7 downto 0); LBx LData In GSBL : in STD LOGIC VECTOR (7 downto 0);

LBx\_LData\_Out\_GSBL : out STD\_LOGIC\_VECTOR (7 downto 0):

LBx\_Latch\_DB\_DIR : in STD\_LOGIC;

LBx\_LStatus\_In\_LGSB : in STD\_LOGIC\_VECTOR (1 downto 0); LBx\_LStatus\_Out\_LGSB : out STD\_LOGIC\_VECTOR (1 downto 0);

LBx\_LStatus\_In\_GSBL : in STD\_LOGIC\_VECTOR (1 downto 0);

LBx LStatus Out GSBL : out STD LOGIC VECTOR (1 downto 0); LBx\_Latch\_SB\_DIR : in STD\_LOGIC;

LBx\_LCtrl\_In\_LGSB : in STD\_LOGIC\_VECTOR (5 downto 0);

LBx\_LCtrl\_Out\_LGSB : out STD\_LOGIC\_VECTOR (5 downto 0);

LBx\_LCtrl\_In\_GSBL : in STD\_LOGIC\_VECTOR (5 downto 0);

LBx\_LCtrl\_Out\_GSBL : out STD\_LOGIC\_VECTOR (5 downto 0): LBx\_Latch\_CB\_DIR : in STD\_LOGIC

);

# 7. RESULT

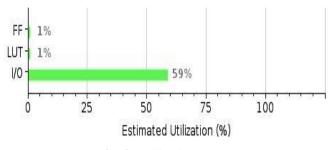

# 7.1 Utilization Graph

Fig -9: Utilization Graph

#### 7.2 Utilization Table

118

1/0

| Table -1: Utilization Table |            |           |               |  |  |  |

|-----------------------------|------------|-----------|---------------|--|--|--|

| Resource                    | Estimation | Available | Utilization % |  |  |  |

| FF                          | 16         | 106400    |               |  |  |  |

| LUT                         | 278        | 53200     |               |  |  |  |

200

1

59

# 7.3 Behavioral Simulation of Switch Box

| 09-june-2014 - [/home/anoop/MM                                         |            | •        |                                                                           | Vivado 20      | 013.4      |                  |           |        |             |          | ₩ \$     | ◇ �)) 11: | 14 PM 👤 Anoo |             |                 |

|------------------------------------------------------------------------|------------|----------|---------------------------------------------------------------------------|----------------|------------|------------------|-----------|--------|-------------|----------|----------|-----------|--------------|-------------|-----------------|

| <u>File Edit</u> Flow <u>T</u> ools <u>W</u> indow L                   |            |          |                                                                           | _              |            |                  |           |        |             |          |          |           | Q+ Searc     | h comman    | ds              |

| 🯄 🔁 🕼 💵 🗎 🐘 🗙 🔌 🛉                                                      |            | 8        | 🖌 🔀 🥵 😬 Default Layout 👘 🦄                                                | <u>,</u> ∭ ∲ , | 🖹 🕅        | <b>≥</b> (†) 100 | ) ns 🔹 🧏  |        | <b>(2</b> ) |          |          |           |              |             | Read            |

| Flow Navigator «                                                       | B          | ehav     | ioral Simulation - Functional - sim                                       | _1 - Switch    | _Вох       |                  |           |        |             |          |          |           |              |             | >               |

| < 꽃 🖨                                                                  |            |          | Untitled 2* ×                                                             |                |            |                  |           |        |             |          |          |           |              |             | ðĽ×             |

| Project Manager     G Project Settings                                 | , Objects  | *)<br>   | Name                                                                      | Value          |            | 068 pc           | 11 070 pc | 11     | 072 pc      | 11 074 - | 15       | 1 076 pc  | 11 078 pc    | 11 080 5    | e 11            |

| Add Sources                                                            | 4          | 0+       | 4 ISBC ISB SB DIR                                                         | 0              |            | ,068 ns          |           | uu ¦'i |             | 1,0,4,1  | Ľ        |           | 1,078 ns     | 1,080 n     | <u>'''''</u> '' |

| F IP Catalog                                                           | es         |          | <ul> <li>ISBC_TO_ISB_SBS(3:0)</li> <li>ISBC_Frm_ISB_SBS(3:0)</li> </ul>   | 0000<br>1111   |            |                  |           |        |             | 0000     |          |           |              |             |                 |

| <ul> <li>IP Integrator</li> </ul>                                      | Properties | 0        | •                                                                         | 0              |            |                  |           |        |             | 0        |          |           |              |             |                 |

| at Create Block Design                                                 | Lop        | <u> </u> | •                                                                         | aaaa           |            |                  |           |        |             | aaaa     | ,        |           |              |             |                 |

| Den Block Design                                                       |            | M        | <ul> <li>LSB_DataBus00[7:0]</li> </ul>                                    | aa             |            |                  |           |        |             | aa       |          |           |              |             |                 |

| 🐁 Generate Block Design                                                |            |          | <ul> <li>LSB_CntlBus00[5:0]</li> </ul>                                    | 00             |            |                  |           |        |             | 00       |          |           |              |             |                 |

|                                                                        |            | Ċ        | <ul> <li>LSB_StatusBus00[1:0]</li> </ul>                                  | 0              |            |                  |           |        |             | 0        |          |           |              |             |                 |

| Simulation                                                             | Scope      | 2        | •\LSB_AddrBus_IN01(15:0)                                                  | CCCC           |            |                  |           |        |             | cccc     |          |           |              |             |                 |

| 🚳 Simulation Settings                                                  |            | a        | •LSB_DataBus01(7:0)                                                       | сс             |            |                  |           |        |             | cc       |          |           |              |             |                 |

| 🔍 Run Simulation                                                       |            | - C      | •-LSB_CntlBus01[5:0]                                                      | 01             |            |                  |           |        |             | 01       |          |           |              |             |                 |

| A RTL Analysis                                                         | ~          |          | •-LSB_StatusBus01[1:0]                                                    | 1              |            |                  |           |        |             | 1        |          |           |              |             |                 |

| Den Elaborated Design                                                  |            |          | <ul> <li>➡ LSB_AddrBus_IN02[15:0]</li> <li>►LSB_DataBus02[7:0]</li> </ul> | bbbb<br>bb     |            |                  |           |        |             | bbbb     | )        |           |              |             |                 |

| , E open Laborated Design                                              |            |          | •-LSB_Databus02[7:0]                                                      | 02             |            |                  |           |        |             | 02       |          |           |              |             |                 |

| <ul> <li>Synthesis</li> </ul>                                          |            | ζ,ι      | •-LSB_StatusBus02[1:0]                                                    | 2              |            |                  |           | -      |             | 2        |          |           |              |             |                 |

| 🔞 Synthesis Settings                                                   |            |          | •                                                                         | dddd           |            |                  |           |        |             | dddo     | ł        |           |              |             |                 |

| 🔈 Run Synthesis                                                        |            |          | •-LSB DataBus03[7:0]                                                      | dd             |            |                  |           |        |             | dd       |          |           |              |             |                 |

| 👂 💕 Open Synthesized Desig                                             |            |          | <ul> <li>LSB_CntlBus03[5:0]</li> </ul>                                    | 03             |            |                  |           |        |             | 03       |          |           |              |             |                 |

| <ul> <li>Implementation</li> </ul>                                     |            |          | LSB_StatusBus03[1:0]                                                      | 3              |            |                  |           |        |             | 3        |          |           |              |             |                 |

| <ul> <li>Implementation</li> <li>Implementation Settings</li> </ul>    |            |          | • 📲 GSB_AddrBus_OUTPUT[15:0]                                              | aaaa           | X000X      | aaaa             | XXXXX (   | bbbb   | <u>) x</u>  | XXX      | ( cccc   | )000X     | aaaa         |             | bbbb            |

| Run Implementation                                                     |            |          | •GSB_DataBus(7:0)                                                         | аа             | XX         | aa               |           | bb     |             | XXX      | <u> </u> | XX        | aa           |             | bb              |

| <ul> <li>Run implementation</li> <li>Open implemented Desir</li> </ul> |            |          | <ul> <li>GSB_CntlBus[5:0]</li> </ul>                                      | 00             | 0X         | 00               | OX X      | 02     |             | 0×       | 01       | 0X        | 00           | OX )        | 02              |

| <ul> <li>Open implemented Desir</li> </ul>                             |            |          | •-GSB_Statusbus[1:0]                                                      | 0              | <u>x (</u> | 0                |           | 2      | X           | X        | ()       | Х         | 0            |             | 2               |

| Program and Debug                                                      |            |          |                                                                           |                |            |                  |           |        |             |          |          |           |              |             |                 |

| 🍪 Bitstream Settings                                                   |            |          |                                                                           |                | •          |                  |           |        |             |          |          |           |              |             |                 |

| 🚵 Generate Bitstream 🛛 🖃                                               |            |          |                                                                           |                |            |                  |           |        |             |          |          |           |              |             |                 |

| 🖒 📑 Onen Hardware Manage                                               |            | -        | Fcl Console 🔎 🖳                                                           |                |            |                  |           |        |             |          |          |           |              |             |                 |

| Binary                                                                 |            |          |                                                                           |                |            |                  |           |        |             |          |          |           | 9            | Sim Time: 3 | 100 ns          |

# 7.4 Synthesis Report

| Synthesis |                                  | * |

|-----------|----------------------------------|---|

| Status:   | 💞 Complete                       |   |

| Messages: | 8 critical warnings              |   |

|           | () 135 warnings                  |   |

| Part:     | xc7z020clg484-1                  |   |

| Strategy: | <u>Vivado Synthesis Defaults</u> |   |

# 7.5 DRC Report

# DRC Violations

Summary: 0 o errors 1 2 critical warnings 1 128 warnings 0 advisories

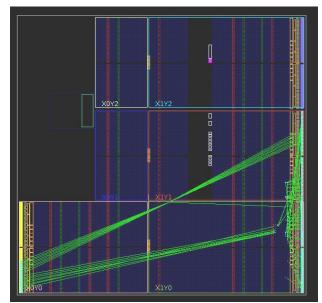

# 7.6 Implementation Report

| Implementation         | \$ |  |

|------------------------|----|--|

| Conflict nets:         | 0  |  |

| Unrouted nets:         | 0  |  |

| Partially routed nets: | 0  |  |

| Fully routed nets:     | 10 |  |

| Summary Route Status   |    |  |

# 7.7 Timing Report

\$

| Timing                       | \$          |  |

|------------------------------|-------------|--|

| Worst Negative Slack (WNS):  | 0 ns        |  |

| Total Negative Slack (TNS):  | 0 ns        |  |

| Number of Failing Endpoints: | 0           |  |

| Total Number of Endpoints:   | 0           |  |

| Setup Hold Pulse Width       |             |  |

| Post-Synthesis Post-Imp      | lementation |  |

\$

# 7.8 Power Report

| ower                                |                |  |

|-------------------------------------|----------------|--|

| Total On-Chip Power:                | 0.13 W         |  |

| Junction Temperature:               | 26.5 °C        |  |

| Thermal Margin:                     | 58.5 ℃ (4.9 W) |  |

| Effective θJA:                      | 11.5 °C/W      |  |

| Power supplied to off-chip devices: | 0 W            |  |

| Confidence level:                   | Low            |  |

Summary On-Chip

# 7.9 Power Summary (Graph)

Fig -9: Power Summary

#### 7.10 Implemented Design

Fig -10: Implemented Design

#### 8. CONCLUSIONS

In the above result, architecture of intelligence switch box for bus arbitration and its synchronization for multi microcontroller embedded system on programmable chip for address bus, data bus, control bus and status bus is successfully done.

Also the algorithm for synchronization of address bus, data bus, control bus and status bus for multi-microcontroller embedded system on programmable chip at a master clock frequency of 10-12 MHz for all microcontrollers and slave clock frequency of 100 MHz for tri-state buffers is proposed. The proposed algorithm and techniques are as:

#### Algorithm:

|                                 | Propagation | $delay(P_d$          | )+Constant | timing |

|---------------------------------|-------------|----------------------|------------|--------|

| delay( $C_{td}$ )<br>Switch 01: | Propagation | delay(P <sub>d</sub> | )+Constant | timing |

| delay(Ctd)                      |             | • • -                |            | -      |

| Switch 10: $delay(C_{td})$      | Propagation | delay(P <sub>d</sub> | )+Constant | timing |

|                                 | Propagation | delay(P <sub>d</sub> | )+Constant | timing |

| delay(C <sub>td</sub> )         |             |                      |            |        |

#### **Techniques:**

Switch (0-3): Number of NOT Gate ( $P_d$ )+Constant Timing Delay ( $C_{td}$ )

Switch 00: 0 ( $P_d$ ) + 1ns ( $C_{td}$ ) Switch 01: 3 ( $P_d$ ) + 3ns ( $C_{td}$ ) Switch 10: 8 ( $P_d$ ) + 5ns ( $C_{td}$ ) Switch 11: 13 ( $P_d$ ) + 7ns ( $C_{td}$ )

Hence, the proposed algorithm and techniques getting verified and tested for global bus synchronization using multi-clock and multi phases DLL (Delay Lock Loop).

$\begin{array}{l} \Delta P_{dsw0-1} = 3 \Delta C_{tdsw0-1} = 2 ns \\ \Delta P_{dsw1-2} = 5 \Delta C_{tdsw1-2} = 2 ns \\ \Delta P_{dsw2-3=} 5 \Delta C_{tdsw2-3} = 2 ns \end{array}$

The prototyping & verification has been done using following tools & technology by considering various design constraints:

#### Software operating environment:

- Operating System: UBUNTU 12.04 LTS

- Hardware Design Software: Vivado 2013.4

- Modeling and Simulation Software: Vivado 2013.4, ISim

- Synthesis Software: Compiler-II

- Static Timing Analyzer: Prime-Time

- Power Analyzer: XPA

- Power Estimator: XPE

#### Hardware Prototyping Environment:

- FPGA Device: Zynq-7000 (Ultra-Fast and Ultra-Low-Power)

- Zynq-7000 FPGA Device Series: xc7z020clg484-1

- Device Technology: 28nm

- Device Category: General Purpose

- Clock Frequency: 50 Hz to 1GHz

- Speed Grade: -1

- No. of Pins: 484

- Operating Voltage: 1.16 V

- Operating Temperature:  $-20^{\circ}$  C to  $80^{\circ}$  C

- Operating Clock Frequency: 10MHz and 15-20 MHz

#### REFERENCES

- [1] Benini, L. and De Micheli, G.,2002. Networks on Chips: A new SoC paradigm. IEEE Computer, 35(1), 2002; 70-78.

- [2] Terry Tao Ye 2003. On-Chip Multiprocessor Communication Network Design And Analysis PhD thesis, Stanford University.

- Beltrame G., Sciuto, D., Silvano. C., Paulin, P.and Bensoudane,E.,2006. An application mapping Methodology and case study for multi-processor on -chip architectures.Proceeding of VLSI SoC 2006. 16-18 October 2006, Nice.France 146-151.

- [4] T. S. Rajesh Kumar 2008. On-Chip Memory Architecture Exploration of Embedded System on Chip PhD thesis Supercomputer Education and Research Centre Indian Institute of Science, Bangalore, India.

- [5] Xue, L., Ozturk, O., Li.F. Kandemir, M. and Kolcu. I.,2006.Dynamic partitioning of processing and memory resources in embedded MPSoC architectures .Proceeding of DATE 2006, 6-10 March 2006, Munich, Germany, 690-695.

- [6] Benini L. and De Micheli, G., 2006. Networks on Chips: Technology and tools. Morgan Kaufmann, San Francisco, 2006, ISBN-10:0-12-370521-5.

- [7] L. Benini, D. Bertozzi, D. Bruni, N. Drago, F. Fummi, M. Poncino, "SystemC Cosimulation and Emulation of Multiprocessor SoC Designs", IEEE Computer, Volume: 36 Issue: 4, April 2003.

- [8] F. Poletti, D. Bertozzi, A. Bogliolo, L. Benini, "Performance Analysis of Arbitration Policies for SoC Communication Architectures", Journal of Design Automation for Embedded Systems, pp.189-210, Vol. 8, June/Sep 2003.

- [9] A novel on-chip communication network .Proceeding of International Symposiumon Systemon-Chip, 16-18 November 2004.

- [10] Advance Computer Architecture, Parallelism, Scalability, programmability by Kai Hwang.

- Ha, S., 2007. Model-based programming environment of embedded software for MPSoC. Proceeding of ASP-DAC'07, 23-26 January 2007, Yokohamma, Japan, 330-335.

- [12] Jerraya, A. and Wolf W., 2005. Hardware-software interface codesign for embedded systems. Computer, 38(2), February 2005; 63-69.

- [13] Jerraya, A., Bouchhima, A and Petrot, F., 2006. Programming models and HW/SW interfaces abstraction for Multi- Processor SoC. Proceeding of DAC 2006 .San Francisco.USA, 280-285.

- [14] Angiolini, F., Ceng, J., Leupers, R., Ferrari, F., Ferri, C., and Benini, L. 2006. An integrated open framework for heterogeneous MPSoC design space exploration. In Proceedings of the Design, Automation and Test in Europe (DATE'06), 1145-1150.

- [15] Erbas, C. 2007. System-level modeling and design space exploration for multiprocessor system-onchip architectures. PhD thesis, Amsterdam University Press, Amsterdam, the Netherlands.

- [16] Jia, Z. J., Pimentel, A. D., Thompson, M., Bautista, T., and Nunez, A. 2010. NASA: A generic infrastructure for system-level MPSoC design space exploration. In Proceedings of the IEEE 8th Workshop on Embedded systems for Real time Multimedia, 41-50.

- [17] Jia, Z. J., Bautista, T., Nunez, A., Guerra, C., and Hernandez, M. 2008. Design space exploration and performance analysis or the modular design of CVS in a heterogeneous MPSoC. In Proceedings of the Conference on Reconfigurable Computing and FPGA (ReConFig'08). 193-198.

- [18] Martin, G. 2006, Overview of the MPSoC design challenge. In Proceedings of Design Automation Conference (DAC'06).

#### BIOGRAPHIES

He did his B. Tech. (Electronics and Telecommunication Engineering) from UPTU Lucknow, M. Tech. (pursuing) in Electronics and Communication Engineering from UPTU Lucknow. His research interests

include Embedded System Design, System-On-Chip Design.

He did his B. Tech. (Electronics and Communication Engineering), M. Tech. (Computer Science & Engineering), PGD(VLSI Design), Ph.D doing in Computer Science and Engineering. He is

IEEE affiliate of Circuit and System Society and membership of IEEE organization. He is also ACM affiliate of Embedded Computing System of Association of Computing Machine. His research interests include Embedded System Design, System-On-Chip Design, VLSI Design, Advance Computer Architecture Design, RTOS Design, MPSOPC Design, FPGA Design based Embedded System.